フォン・ノイマン型アーキテクチャ

構成

フォン・ノイマン型のアーキテクチャでは、単一のメモリに命令とデータを保存する方式です。現在のコンピュータは基本的にはノイマン型のアーキテクチャを採用しています。プログラム内蔵方式と呼ばれたりもします。

フォン・ノイマン型のコンピュータは以下のように、命令が実行されます。

コンピュータは

①メモリから命令をフェッチし、

②命令をデコードしどんな命令を実行するかを解釈し、

③実行

という流れで命令を実行する。

フォン・ノイマンボトルネック

この方式が考案された当初はCPUクロックとメモリの読み出し/書き出し速度はそれほど大差はなく、問題はありませんでした。しかし、CPUクロックが上昇する方向に性能改善が行われた一方で、メモリに関しては大容量化を優先したため、CPUクロックとメモリの読み書き速度に大きく差が出るようになってしまいました。

そのため、メモリフェッチが行われる間にCPUは何回も命令が実行できてしまうため、メモリフェッチを待つための無駄な時間が存在してしまいます。これをフォン・ノイマンボトルネックと呼びます。

ハーバードアーキテクチャ

フォン・ノイマンボトルネックを改善するために考案されたのがハーバードアーキテクチャです。考案された当時のコンピュータは単一プログラムの実行が主な目的で、現在のように複数プログラムを動作するようなことはありませんでした。そのため、命令をメモリから読むこととデータをメモリから読むことは競合しないので、データ用メモリと命令メモリと複数を持たせるようにすれば、(並列して行えるため)高速化が可能であるというのが特徴です。

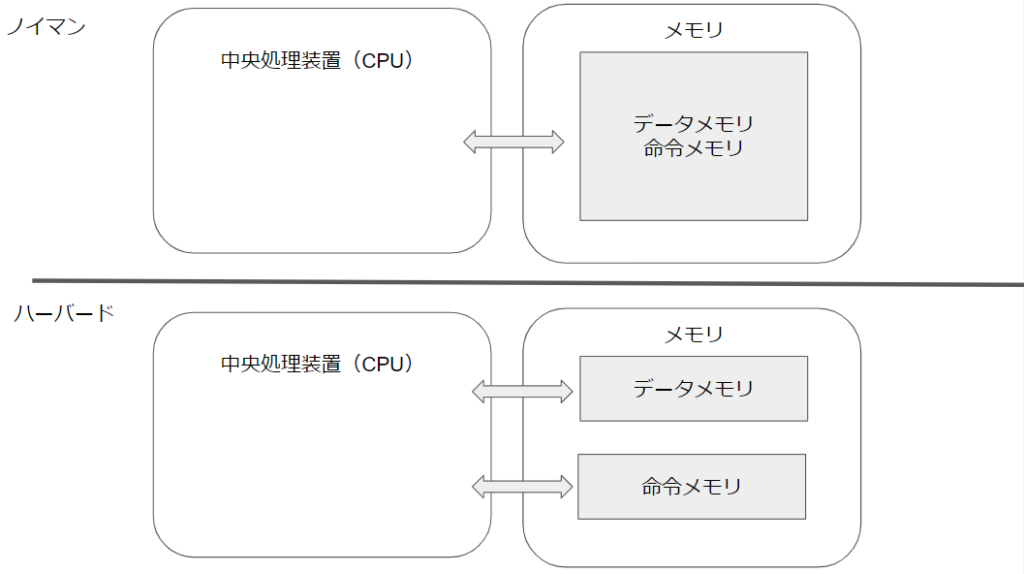

以下にフォン・ノイマンアーキテクチャとハーバードアーキテクチャと構成図を示します。

まとめると、ハーバードアーキテクチャでは、2つのメモリを使用し、命令データとデータの保存先のメモリを別々にする方式です。DSP(Digital Signal Processor)やマイコンなどの組込み用途向けのコンピュータでは、ハーバードアーキテクチャを採用していることがあります。

必ずしも命令を命令メモリ、データをデータメモリに保存する必要はなく、高速化のために必要に応じて分けて命令メモリにデータを置くこともあります。

例えば、FIRフィルタなどのフィルタ計算では、係数データと状態データの積和を計算します。このとき、係数データと状態データを別々のメモリに置いたとします。このとき、1度で係数データと状態データを取り出せることができるので、高速化が期待できます。

まとめ

フォン・ノイマンアーキテクチャは、単一のメモリにデータと命令を置く方式です。一方で、ハーバードアーキテクチャはメモリと命令を別々のメモリに置く方式です。

コメント