AXI4-Lite 概要

AXI4-Liteバスは、アドレスを使用した書き込み、および読み取りを必要とする通信が必要な場合、最も単純な実装はAXI4-Liteになります。

AXI4-LiteはAXI4の簡易版という立ち位置です。主に制御レジスタへの書き込み、ステータスレジスタの読み取り、メモリの読み取りと書き込みに使用されることが多いです。

AXI4バスをより単純な形式で実現するため、いくつかの制限があります。

1つ目は、トランザクションごとに1つのデータの読み込み、あるいは書き込みが可能だということです。つまり、AXI4-Liteにはバースト転送は存在しません。

2つ目は、データバスの全ビット幅のみを利用できることです。さらに、そのビット幅は32ビットあるいは64ビットのいずれかであることです。

アプリケーションがこの制限を満たす場合、AXI4バスよりもAXI4-Liteを選択することができます。AXI4よりもシンプルな実装のため、検証およびリソースも少なくて済みます。

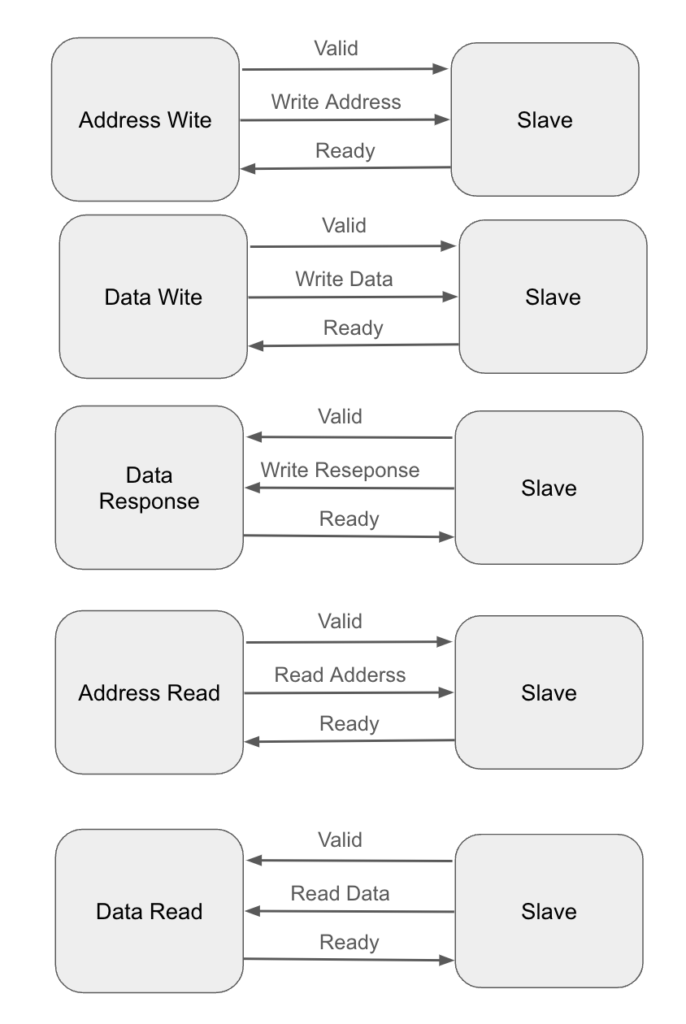

バス構成

AXI4-Liteは実際には5つの独立したバスが使用されます。

- 書き込み用アドレスバス

- 書き込み操作のアドレスをやり取りする

- 書き込み用データバス

- 書き込み操作するデータをやり取りする

- 書き込み用応答バス

- 書き込みが正常に完了したかどうかを応答する

- 読み取り用アドレスバス

- 読み取り操作のアドレスをやり取りする

- 読み取り用データバス

- 読み取り操作のデータをやり取りする

これら5つのバスにそれぞれに同様のReady/Validのハンドシェークが存在します。

複雑なバス構造に見えますが、実際には、操作を単純なトランザクションに分解し、それぞれの操作をバスで分離して行っているだけです。

ハンドシェーク

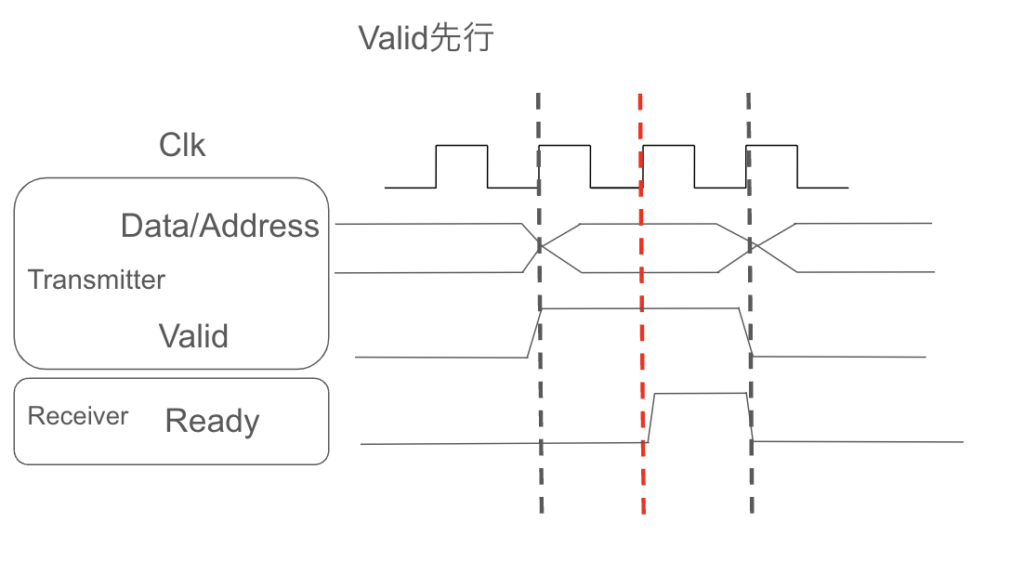

AXI4-Streamと同様にハンドシェークは3つの異なるシナリオを想定する必要があります。Valid先行, Ready先行, Valid/Ready同時の3つのシナリオを考えます。

Valid先行

Valid先行では、アドレス、データあるいは応答を送信するモジュールがバスに値を送信し、それと同時にそれらが有効であることを示すシナリオです。

送信側がValidを先にアサートし、受信側が準備完了を示すReadyがアサートされるのを待ちます。Valid, Readyがどちらもアサートされているクロックサイクルでトランザクションが行われます。

このシナリオでは、受信側がReadyをアサートする前(準備完了前)に、送信側がアドレスまたはデータが有効であることを示します。その後、受信側が準備完了を示すReadyをアサートし、次のクロックの立ち上がりで、アドレスあるいはデータが送信されます。

トランザクションが完了すれば、ValidとReadyはデアサートすることができます。

AXI4-Liteにおいて、バスのマスターとスレーブは、5つのバスのうちどのバスがトランザクションを行なっているかに応じて、送信側と受信側のいずれかになります。

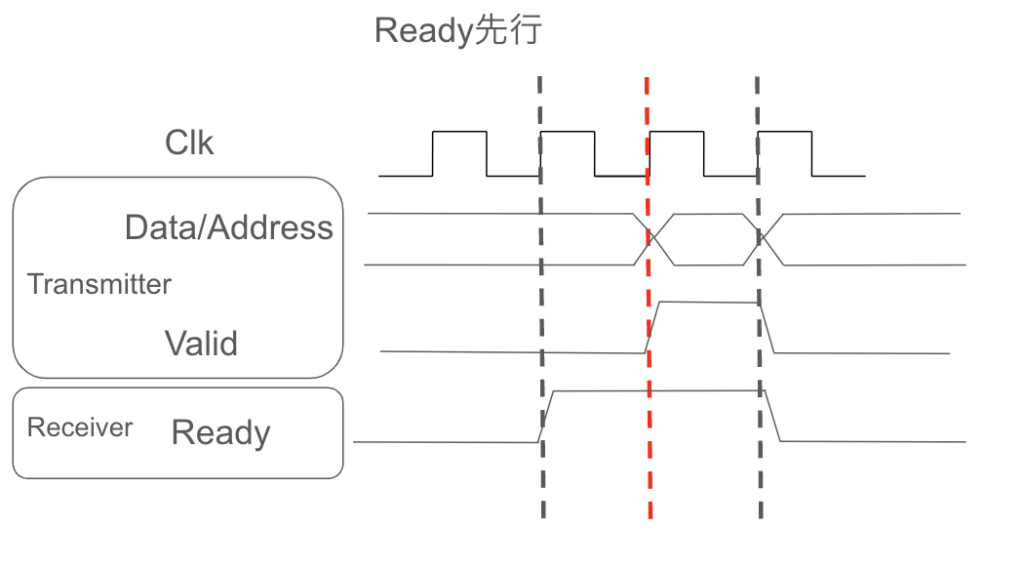

Ready先行

2つめのシナリオは、受信側が先に準備完了であることを示し、その後送信側からValidがアサートされ、有効なデータ、アドレス、応答が送信される場合です。

一般的に、受信側の設計では、送信側がValidをアサートしているかに関わらず、受信側が準備完了ならReadyをアサートし続けて、データを受信できることを示す必要があります。

受信側では、Validがアサートされるまで待機し、次のクロックの立ち上がりでデータ、アドレス、応答を受信します。送信側と受信側が、対応する信号をデアサートし、トランザクションが完了したことを示します。

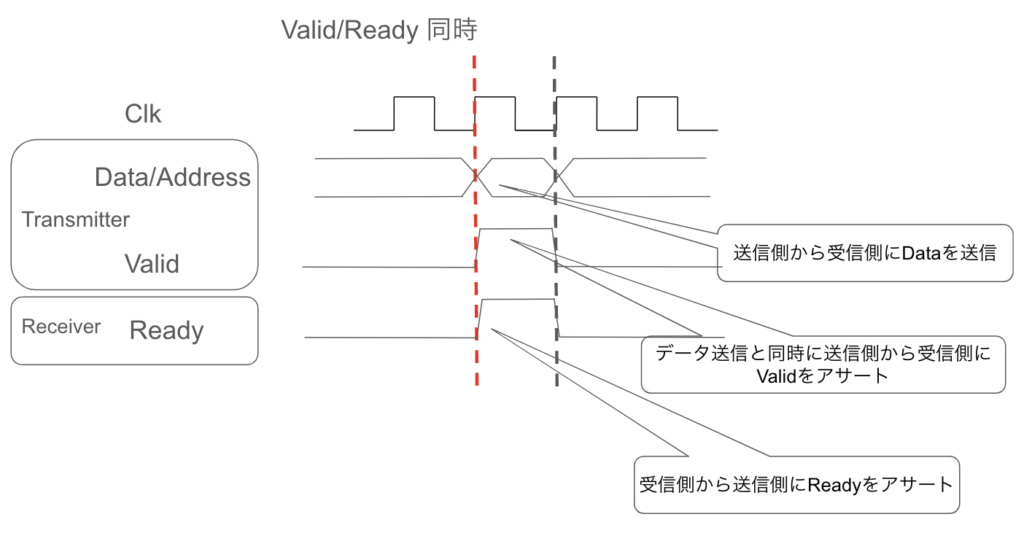

Valid/Ready 同時

3つ目のシナリオは、送信側と受信側が同じクロックサイクルで、Valid, Readyがアサートされるような場合です。これはあまりない状況ですが、トランザクションが成功したことは、両方で認識され、次の立ち上がりのクロックサイクルで、ディアサートされます。

各信号

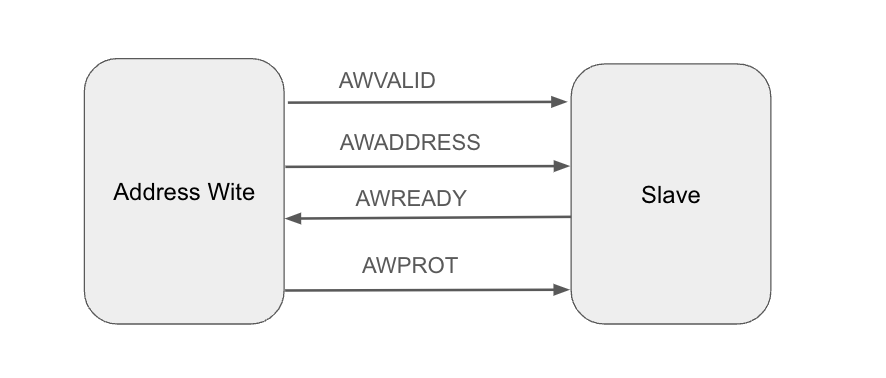

書き込み用アドレスバス

| 信号名 | ソース | 説明 |

| ACLK | Global | クロック信号 |

| ARESETn | Global | リセット信号 アクティブロー |

| AWVALID | Master | マスターからの書き込みアドレスが有効であることを示す |

| AWREADY | Slave | スレーブが書き込みアドレスを受信可能であることを示す |

| AWADDRESS | Master | 書き込みアドレス 1度の書き込み用のアドレス |

| AWPROT | Master | アクセス保護 任意の信号 |

AWADDRESSが実際に書き込むデータを格納するアドレスを示します。

AWprotectと呼ばれる信号は、アクセス保護を提供するオプション信号です。ほとんどのアプリケーションでは任意の信号ですが、設計に何らかの保護機能が必要な場合は、この信号を利用します。

| Prot Bit | 説明 |

| Prot[0] | 0 = 非特権アクセス 1 = 特権アクセス |

| Prot[1] | 0 = 非セキュアアクセス 1 = セキュアアクセス |

| Prot[2] | 0 = データアクセス 1 = 命令アクセス |

マスターはProt信号は3ビット幅で、最初のビットは特権アクセスかどうかを示すビットです。1の場合、特権アクセスであることを示し、0の場合は、非特権のアクセスです。

2ビット目は、セキュアアクセスかどうかを示すビットです。1の場合、セキュアアクセスであることを示し、0の場合は、非セキュアアクセスを示します。

3ビット目は、0の場合データアクセスを示し、1の場合は命令アクセスを示します。

これら全てのビットを使って、マスターからの書き込みアドレスが有効かどうかが決まります。スレーブは、これらの条件を全て満たしているかどうかを確認し、それに応じて書き込みアクセスを拒否することができます。

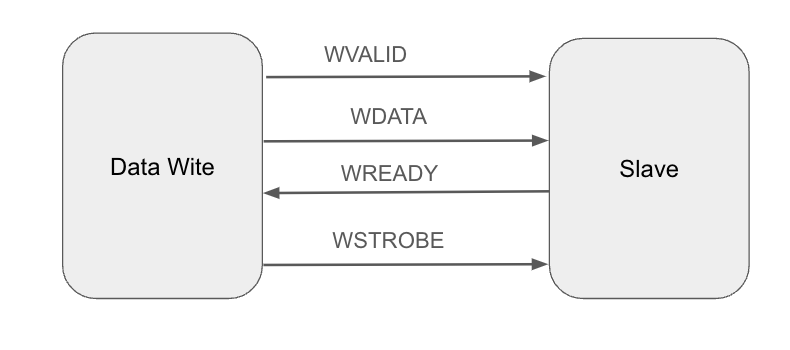

書き込み用データバス

書き込み用アドレスバスによって、送信が可能であれば、書き込み用のデータバスが使用されデータが送信されます。このバスを使用して、実データが転送されます。

| 信号名 | ソース | 説明 |

| ACLK | Global | クロック信号 |

| ARESETn | Global | リセット信号 アクティブロー |

| WVALID | Master | マスターからの書き込みデータが有効であることを示す |

| WREADY | Slave | スレーブが書き込みデータを受信可能であることを示す |

| WDATA | Master | 書き込みデータ 1度の書き込み用のアドレス |

| WSTROBE | Master | データのバイトごとの有効性を示す |

書き込み用アドレスバスと同じACLKを使用します。ARESETnについても、アクティブロー信号であり、同じ信号を使います。

WSTROBE信号は、マスターから送信される信号で、データワードの中でどのバイトが有効かを示す信号です。32bitの場合は4ビット幅、64bitの場合は8ビット幅になります。

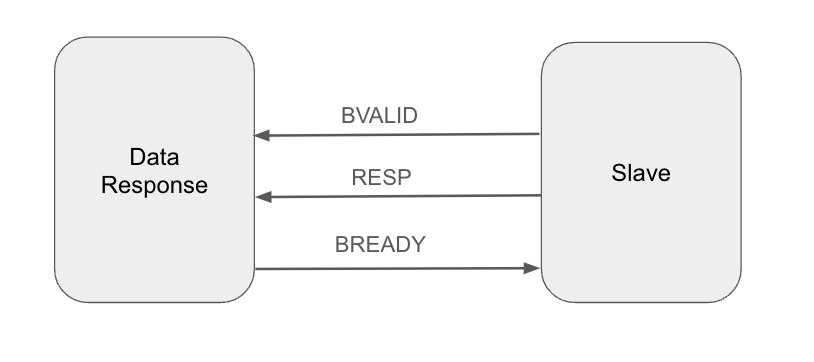

書き込み応答用バス

マスターからの有効なデータとアドレスがスレーブによって受信されると、スレーブはマスターに対して応答する必要があります。これにより、マスターはトランザクションが成功したことを知ることができます。このために書き込み応答用のバスは使用されます。

| 信号名 | ソース | 説明 |

| ACLK | Global | クロック信号 |

| ARESETn | Global | リセット信号 |

| BVALID | Slave | スレーブからの書き込み応答が有効であることを示す |

| BREADY | Master | マスターが応答の受け入れ準備が可能であることを示す |

| BRESP | Slave | スレーブからの応答信号 |

応答は2ビット幅で、応答の意味を表します。

| Response | BRESET[1:0] | 説明 |

| OKAY | 00 | 書き込みが成功 |

| EXOKAY | 01 | 排他アクセスが問題なし |

| SLVERR | 10 | スレーブの範囲内のアドレスが指定されているがエラー |

| DECERR | 11 | スレーブの範囲外のアドレスが指定されていてエラー |

00は書き込みが成功したことを示します。

01は排他アクセスであることを意味します。

10はアドレスが範囲内であるけど、エラーを意味しています。

11はアドレスが範囲外でエラーを示します。

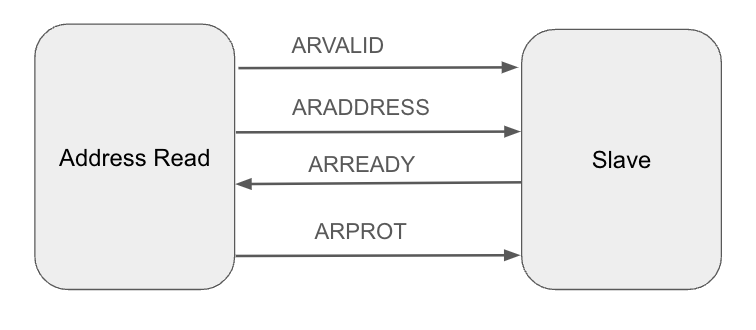

読み出しアドレス用バス

| 信号名 | ソース | 説明 |

| ACLK | Global | クロック信号 |

| ARESETn | Global | リセット信号 |

| ARVALID | Master | マスターから読み出しアドレスが有効であることを示す |

| ARREADY | Slave | スレーブが読み出しアドレスを受信可能であることを示す |

| ARADDRESS | Master | 読み出しアドレス 一度の読み出しで一つのデータの読み出しを行う |

| ARPROT | Master | アクセス保護 任意の信号 |

ACLKとARESETnについては、他のバスと同じものを使用します。

ARPROTはアクセス保護用の信号で、書き込みと同様に読み出し操作にも保護機能があります。

書き込みと同様のビット設定が可能です。

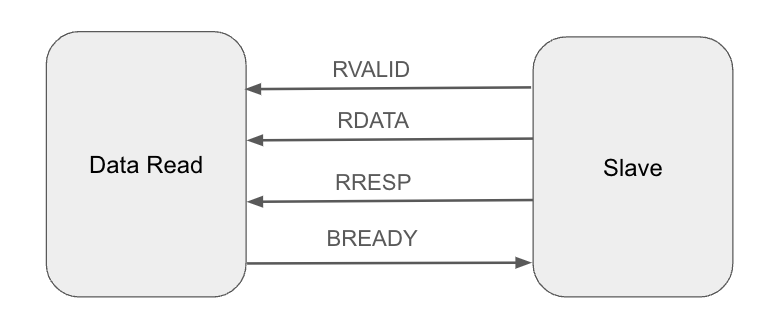

読み出しデータ用バス

| 信号名 | ソース | 説明 |

| ACLK | Global | クロック信号 |

| ARESETn | Global | リセット信号 |

| RVALID | Slave | 読み出しデータが有効であることを示す |

| RREADY | Master | 読み出しデータを受信可能であることを示す |

| RDATA | Slave | 読み出しデータ |

| RRESP | Slave | 読み出し操作の応答 |

読み出し操作の場合、スレーブからのデータ転送と同時に、応答信号もスレーブから転送されます。マスターはこの応用信号から読み出しが成功したかどうかを判断します。

| Response | RRESEP[1:0] | 説明 |

| OKAY | 00 | 読み出しが成功 |

| EXOKAY | 01 | 排他アクセスが問題なし |

| SLVERR | 10 | スレーブの範囲内のアドレスが指定されているがエラー |

| DECERR | 11 | スレーブの範囲外のアドレスが指定されていてエラー |

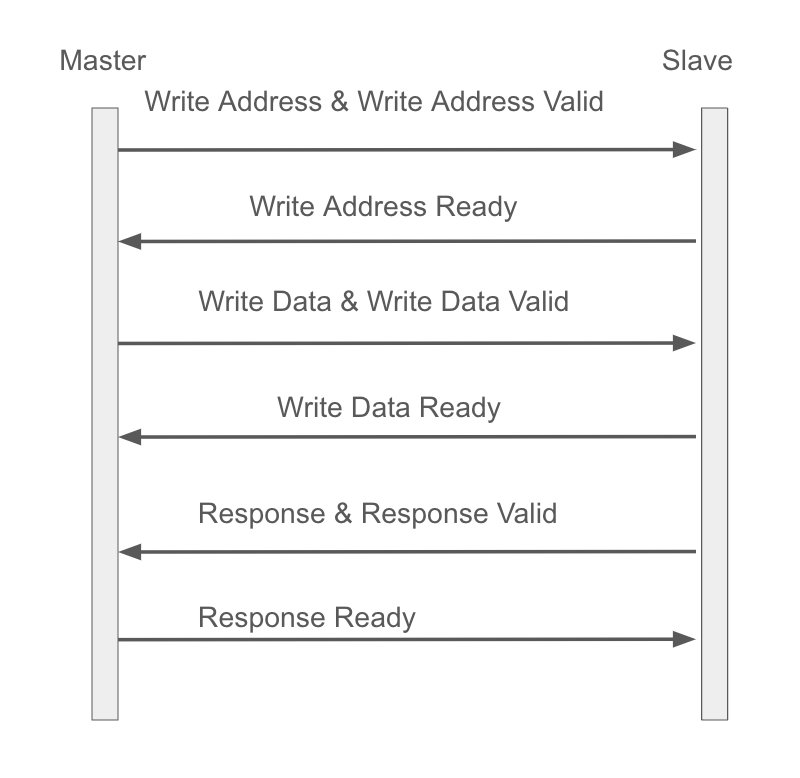

書き込みトランザクション

フロー

AXI4-Liteの書き込みトランザクションを詳しく見ていきます。

書き込みトランザクションは、マスターが書き込みアドレスを転送、Validをアサートすることで開始されます。

次にマスターはスレーブが書き込みアドレスを受信準備完了であることを示すReadyのアサートを待ちます。ReadyとValidの両方がアサートしていれば、アドレスのトランザクションは完了です。

次に、マスターが書き込みデータとValidをアサートします。その後、スレーブがReadyをアサートし、書き込みデータを受信します。

次に、スレーブは書き込みが成功したかどうかを示す応答をマスターに返す必要があります。これはResponseとValidをマスターに送信します。マスターがReadyをアサートすることで応答を受信します。

これで、書き込みトランザクションは完了です。

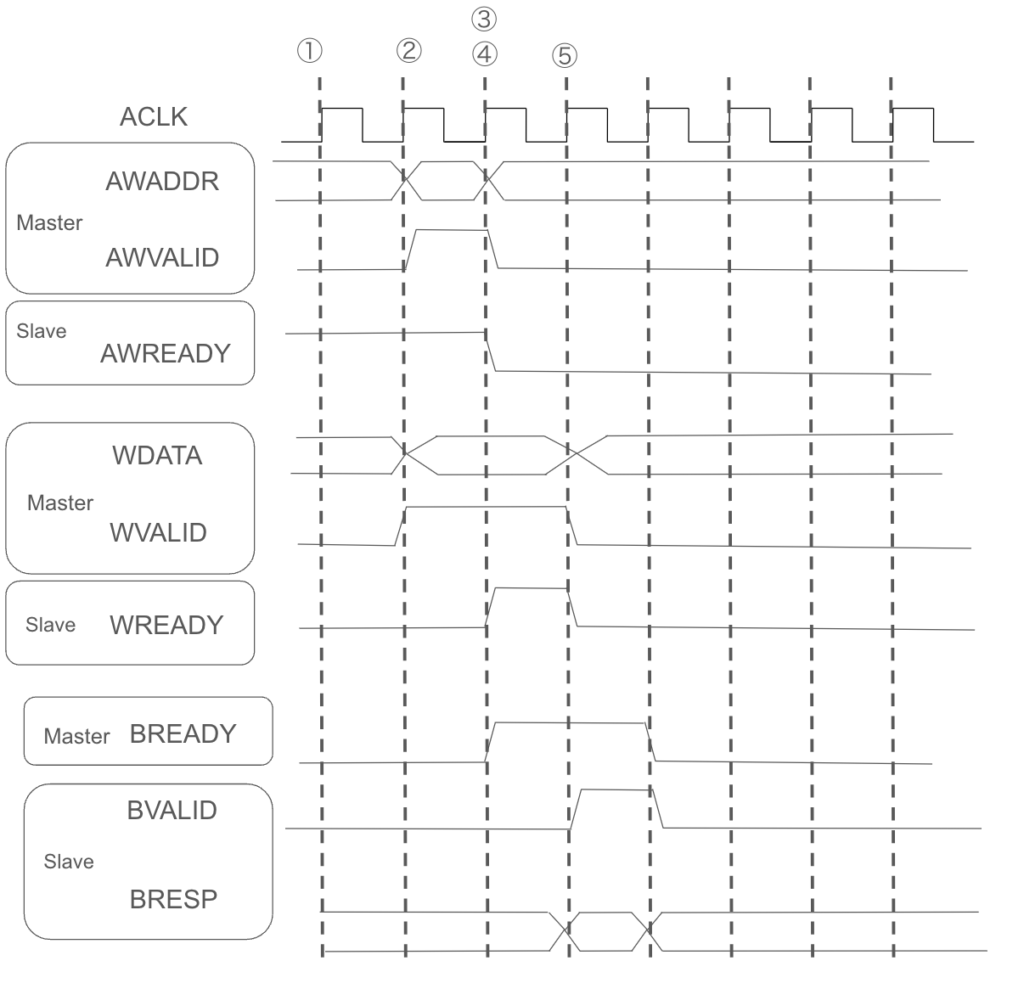

タイミングチャート

典型的な書き込みトランザクションのタイミングチャートを見ていきます。

①スレーブは書き込みアドレスを受信可能な時にReadyをアサートする

②マスターは書き込みアドレスAWADDRを転送する際にAWVALIDをアサートする。それと同時に、書き込みデータWDATAを転送し、WVALIDをアサートする。

③スレーブはデータが受信可能であることをWREADYでアサートする

④マスターはデータおよびアドレスの転送後、応答を受信可能であることを示すためBREADYをアサートする

⑤スレーブは応答データBRESPを転送し、それが有効であることを示すBVALIDをアサートする

書き込みトランザクションの典型的なタイミングチャートを上に示しました。3つのバスは独立しており、互いに依存していないことに注意しましょう。実際のシーケンスは、マスターとスレーブのロジックによって決定されます。

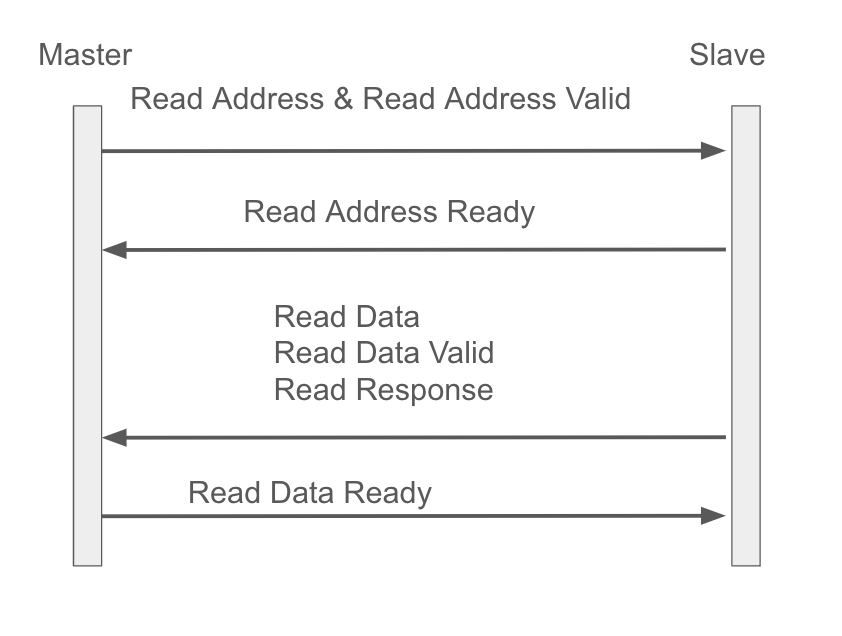

読み出しトランザクション

フロー

読み出しトランザクションは、マスターが読み出しアドレスを転送、Validをアサートすることで開始されます。これは単一のデータを読み取ることができ、保護機能を利用する場合は、それも同時に送信します。

次に、スレーブは読み出しアドレスが受信可能であることを示すReadyをアサートします。

読み取りデータはスレーブが転送し、同時にValidをアサートします。さらに、読み取り操作が成功したかどうかを示すResponseをマスターに転送します。マスターはReadyをアサートすることで転送は完了します。

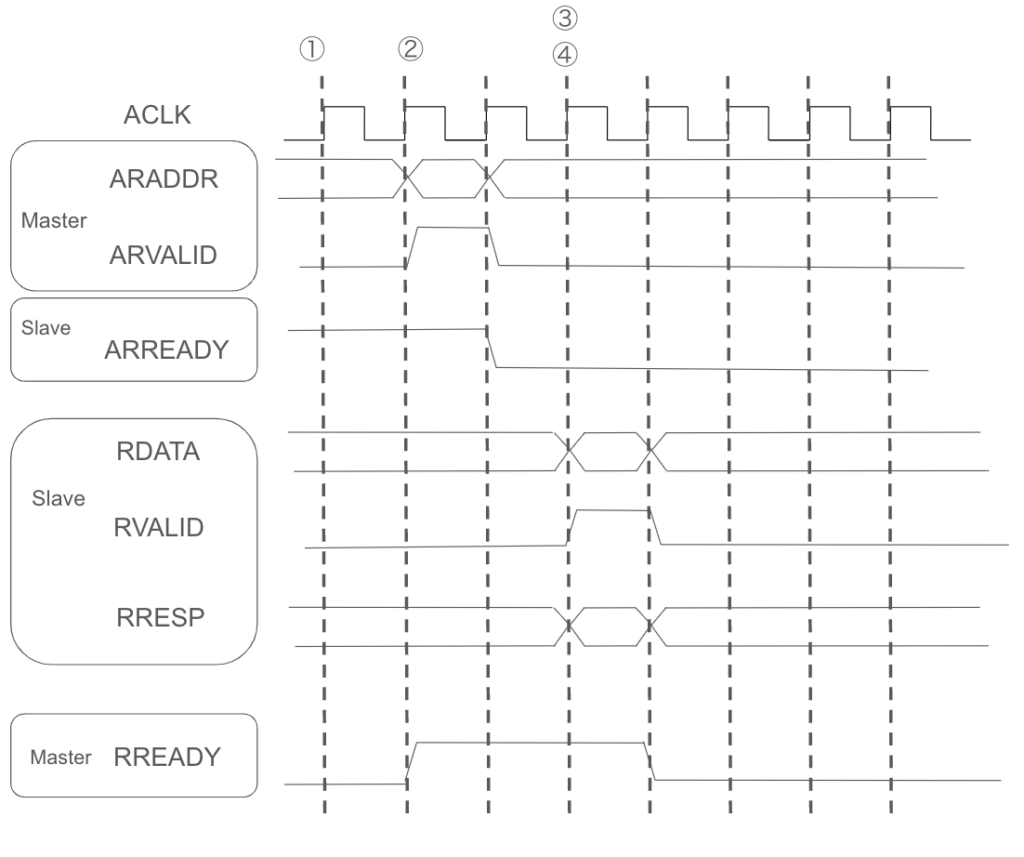

タイミングチャート

①スレーブはアドレスを受信可能であることを示すARREADYをアサートする

②マスターは書き込みアドレスARADDRを転送する際にARVALIDをアサートする。マスターはRREADYをアサートする。

③④ スレーブは読み出しデータおよび応答を転送し、それらが有効であることを示すRVALIDをアサートする

読み出しトランザクションが完了し、RREADY, RVALIDはディアサートされる。

以上が、読み取り操作の典型的なタイミングチャートとなります。

まとめ

本記事では、AXI4-Liteについて解説しました。AXI4-Liteはアドレスを使用した書き込み、および読み取りを必要とする通信が必要な場合に使用することを解説しました。

5つのバスを使用して、書き込み、読み出しトランザクションを実行することをフローおよび典型的なタイミングチャートを用いて説明しました。

コメント