AXI4バスの特徴

AXI4の概要

AXI4バスは、アドレスおよびデータバスが書き込み、読み出しの双方向通信が可能で、それを応答信号によるフロー制御により実現しています。

トランザクションごとに最大256ワードのバースト転送が可能です。ワードサイズは最大で128バイトにすることができます。

このバスは、DMA, プロセッサとの通信、メモリのRead/Write、レジスタのRead/Writeに適しています。

AXI4-Liteとの比較

AXI4では、ワードサイズが128バイトと非常に大きなバス幅が使用可能です。つまり、最大で128 x 256 = 32kBの転送が可能です。

実際に使用できるバス幅は、IPコアやFPGAの構成によって制限 されることがあります。使用するデバイスに応じて、AXI4の最大バス幅が異なるため、具体的な仕様は デバイスのTRM(Technical Reference Manual) を確認するのが確実です。

また、バスの任意の部分が使用可能です。ただし、2の冪乗という制限があります。つまり、2バイト,4バイト, 8バイトのようにすることができます。

一方で、AXI4-Liteではそのような部分的な使用は不可で、全ビット幅を使用する必要があります。また、使用できるビット幅は32ビットと64ビットに限られます。

AXI4では、トランザクションに多くの情報が付随しています。トランザクションID、サービス品質、その他のユーザ情報などAXI4-Liteにはないような情報が追加できます。

| 比較項目 | AXI4 | AXI4-Lite |

| バースト長 | 最大256ワードのバースト転送をサポート | 単一ワードの転送のみサポート |

| データバス幅 | 最大で128バイト (2の冪乗での使用が可能) | 32ビットあるいは64ビット (全ビット幅の使用が必須) |

| 追加情報 | トランザクションID QoS(Quality of Service) ユーザ情報 | サポートなし |

| 使用用途 | DMA, プロセッサ通信, など高機能で大規模な読み書き転送が必要な場合 | レジスタの読み書き, など シンプルな制御で小規模な読み書きの転送が必要な場合 |

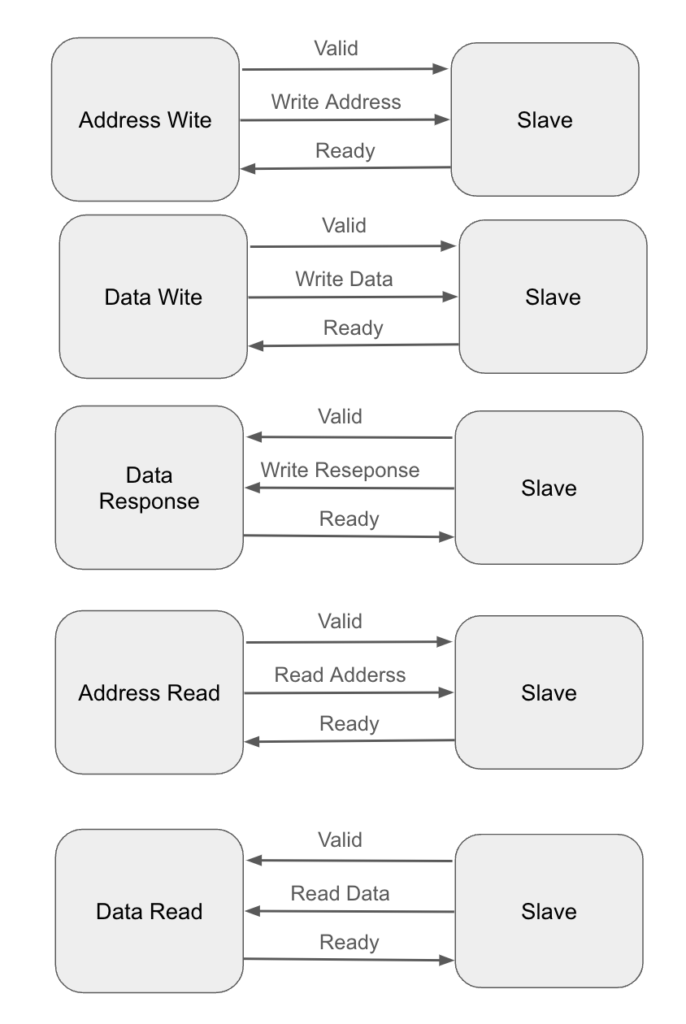

バスの構成

AXI4はAXI4-Liteと同様に5つの独立したバスで構成されています。基本構成は同じです。

- 書き込み用アドレスバス

- 書き込み操作のアドレスをやり取りする

- 書き込み用データバス

- 書き込み操作するデータをやり取りする

- 書き込み用応答バス

- 書き込みが正常に完了したかどうかを応答する

- 読み取り用アドレスバス

- 読み取り操作のアドレスをやり取りする

- 読み取り用データバス

- 読み取り操作のデータをやり取りする

これら5つのバスにそれぞれに同様のReady/Validのハンドシェークが存在します。

複雑なバス構造に見えますが、実際には、操作を単純なトランザクションに分解し、それぞれの操作をバスで分離して行っているだけです。

AXI4バスの仕組み

5つのバスが独立して存在するとパフォーマンスを上げることが可能になります。

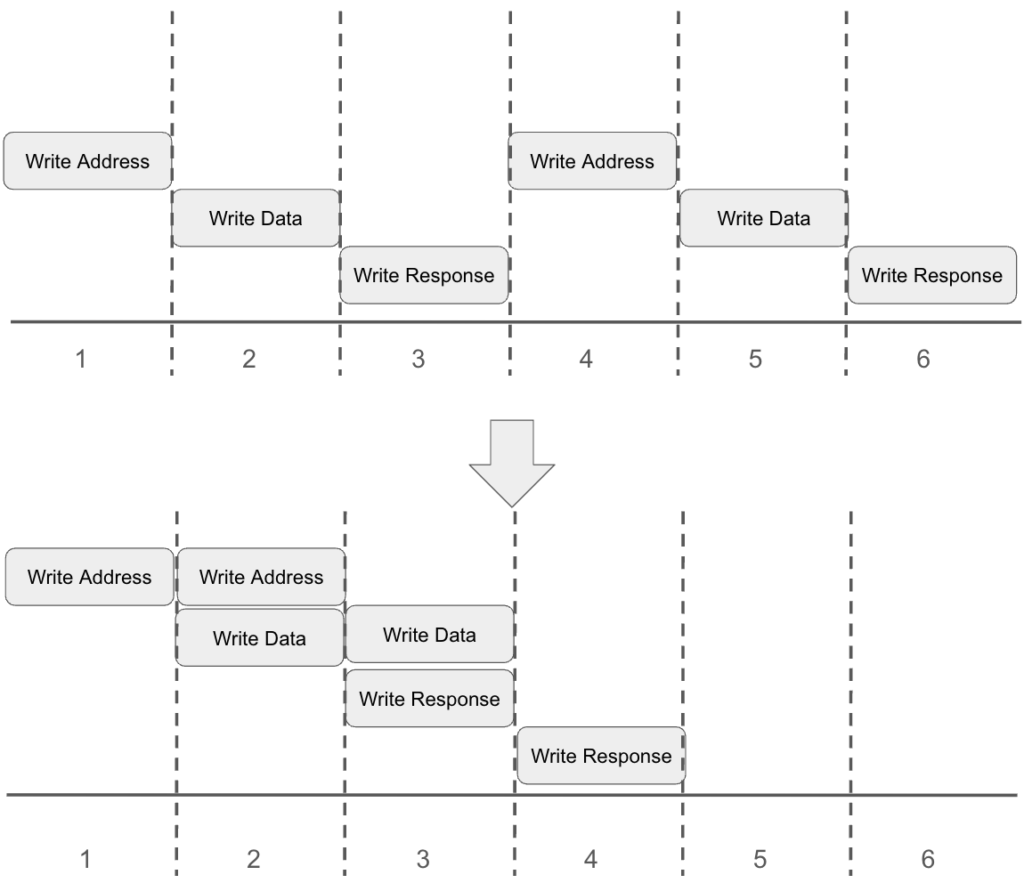

書き込みトランザクションを処理する場合、書き込みアドレスを送信し、次にデータを送信し、応答を待つというシーケンスになります。次のトランザクションも同様になります。

2回書き込みを行うような場合、下の図では上に示すようなトランザクションになります。ここで、AXI4バスは各バスが独立しているため、下の図のようにトランザクションを短縮することができます。

各バスは前のトランザクションが終了することを待つことなく、開始する事ができます。これは書き込みアドレス、データ、応答用バス全てに当てはまります。これは読み出しでも同様です。

したがって、データバスをほとんどの時間帯で使用する事ができるので最大のパフォーマンスを得る事ができます。

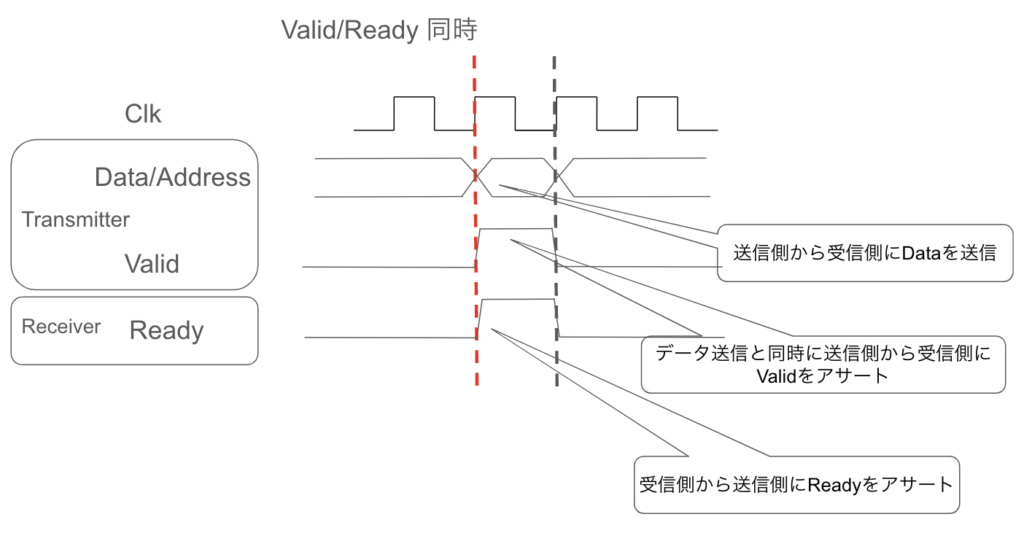

ハンドシェーク

AXI4には、Valid/Readyのハンドシェークが存在します。

各バスごとにこのハンドシェークがあり、3つのシナリオが存在します。

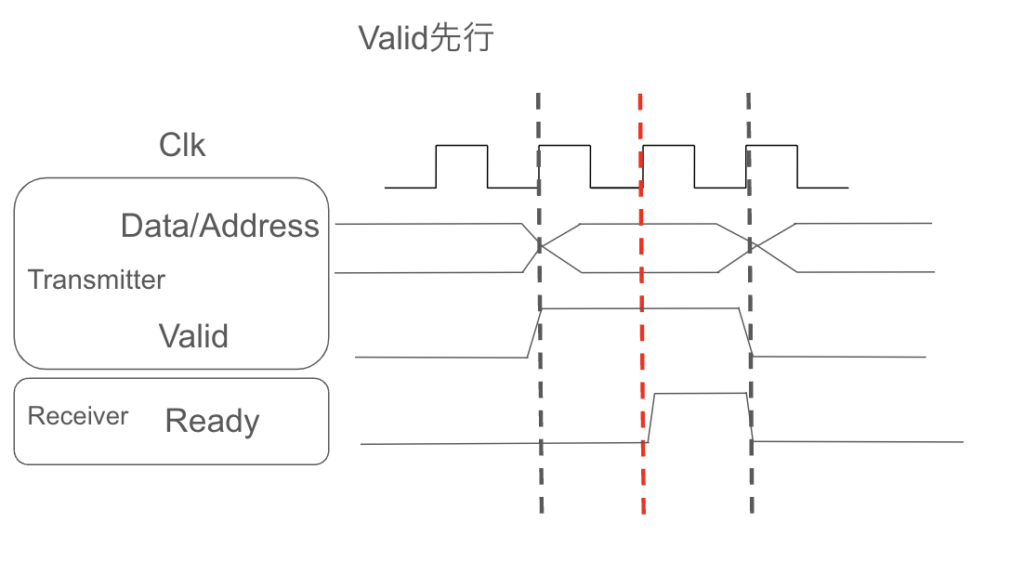

Valid先行

受信側がReadyをアサートする前に、アドレス、データ、または応答を送信するコンポーネントがバスに値を転送し、そしてValidをアサートするようなシナリオです。その後、Readyがアサートされ、転送が完了します。完了すると、ValidとReadyはディアサートされます。

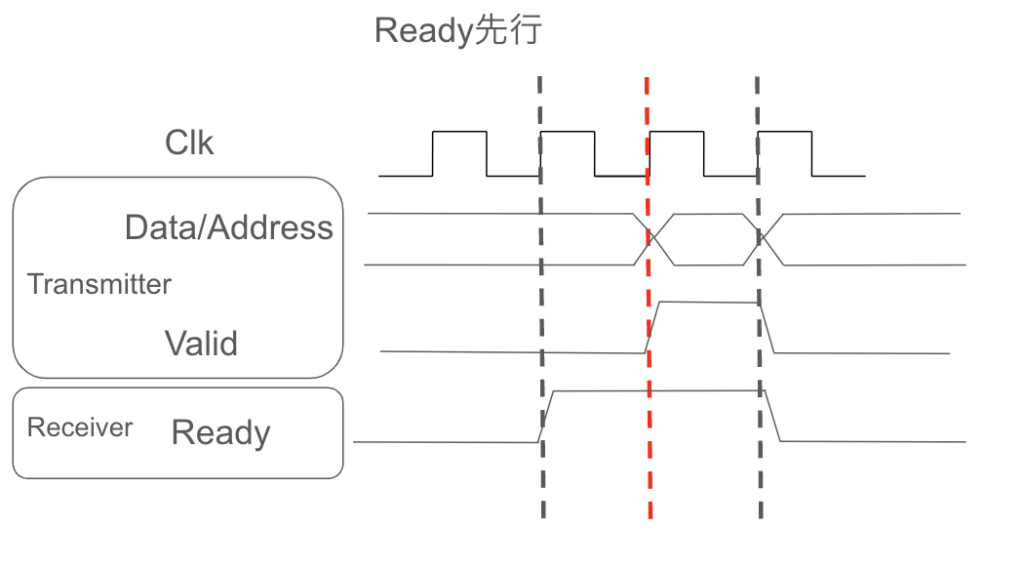

Ready先行

2つ目は、送信側がデータを送信する前に受信側がReadyをアサートするようなシナリオです。一般的に、受信側は、送信側がValidをアサートしているか関係なく、受信準備ができているならReadyをアサートするように設計する必要があります。

受信側はValidがアサートするまで待機し、Validがアサートされたタイミングでデータ、アドレス、応答を受信します。送信側と受信側でValid, Readyをディアサートしてトランザクションが完了したことを示す必要があります。

Valid/Ready同時

3つめは、送信側と受信側が同時にValid, Readyをアサートするような場合です。あまりない状況ですが、トランザクションが成功したことは両側で認識する必要があります。

バス信号

クロックとリセット

クロックとリセット信号は各バスで共通のものを使用し、マスターとスレーブで同じものを使用します。

全ての信号クロックの立ち上がりエッジでサンプリングされます。

リセットはアクティブローで、同期リセット、非同期リセットは設計するデバイスによって決定されます。

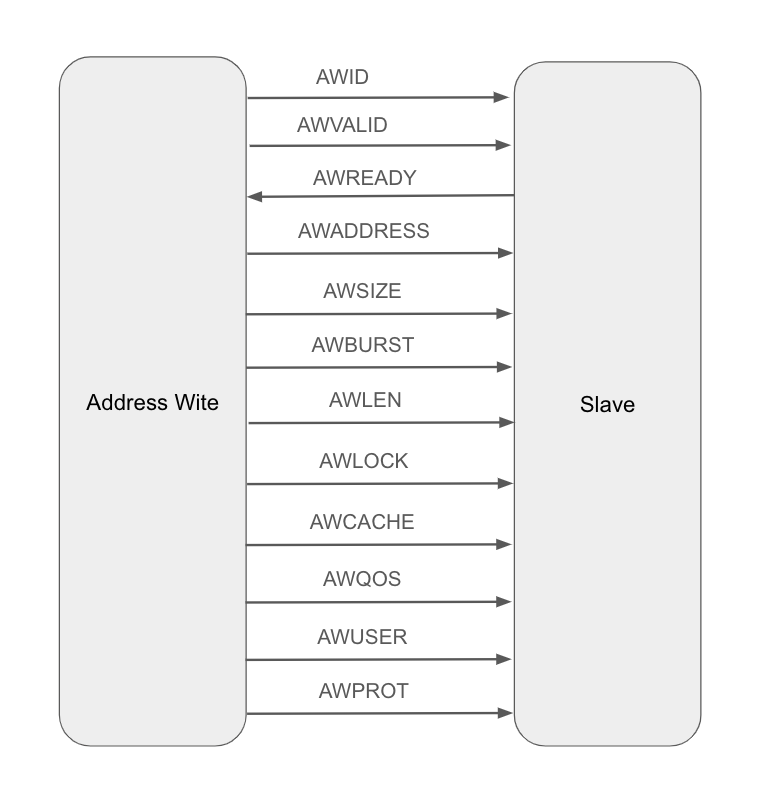

書き込みアドレス用バス

| 信号名 | ソース | 説明 |

| AWID | Master | トランザクションID |

| AWVALID | Master | 書き込みアドレスが有効であることを示す |

| AWREADY | Slave | スレーブが受信可能であること示す |

| AWADDRESS | Master | 書き込みアドレス |

| AWSIZE | Master | バイト中のサブセット 2^AWSIZE, 0 = 1byte, 7 = 128byte |

| AWBURST | Master | バーストタイプ 0 = Fixed 1 = Increment 2 = Wrap 3 = Reserved |

| AWLEN | Master | バースト長 0 = 1, 最大255=256 |

| AWLOCK | Master | アトミックアクセス 0 = ノーマルアクセス 1 = 排他的アクセス |

| AWCACHE | Master | メモリタイプ, バッファ可能, バッファ不可、キャッシュ可能、キャッシュ不可 などを表す信号 |

| AWQOS | Master | ユーザ定義のQOS(Quality of Service)の値 トランザクションのラベル |

| AWUSER | Master | ユーザ定義 |

| AWPROT | Master | アクセス保護, 3ビット幅 1ビット目 1 = 特権アクセス 0 = 非特権アクセス 2ビット目 1 = セキュアアクセス 0 = 非セキュアアクセス 3ビット目 1 = 命令 0 = データ |

AWID

AWIDはトランザクションIDです。

スレーブ(受信側) は、この識別子を元に異なるリクエストを区別し、並列処理が可能になります。

書き込みデータ(Wチャネル)と書き込み応答(Bチャネル)も、AWID に対応する WID および BID で管理されます。

具体的には下記のような用途があります。

- 並列書き込みのリクエスト管理

- 複数のマスターが1つのスレーブへ書き込む場合、トランザクションを識別する

- 例:CPUとDMAコントローラが同じメモリに書き込みする際、それぞれ異なるAWIDを使用し、スレーブ側はAWIDを参照して、どのマスターからのリクエストかを判別し、適切に処理します

- 書き込み順序の最適化

- スレーブがリクエストを並列処理する際、同じAWIDを持つリクエストは順序を維持して、異なるAWIDのリクエストは並列に処理することが可能です

- 書き込み応答との関連付け

- 書き込みが完了すると、スレーブはBIDを含む応答をマスターへ送信します。BIDはAWIDと一致し、どのリクエストの応用かを識別可能になります

ADADDRESS

AWADDRESSは、書き込みアドレスに相当し、バースト転送の場合はベースアドレスになります。

AWSIZE

AWSIZEは、このトランザクションに使用するバス幅を決定します。つまり、バスのある部分(サブセット)を使用することを意味します。多くの場合、バス全体を利用して通信しますが、サブセットを使用する場合は、バスのどのバイトを使用するかを指定することができます。ただし、そのサブセットは2の冪乗のバイトである必要があります。

AWBURST

AWBURSTはバースト転送の際のアドレス更新方法を示します。

00はFixedは同じアドレスに書き込みます。特定のレジスタに書き込むような場合は、このタイプを使用します。

11はIncrementは通常のバースト書き込みで、ベースアドレスからデータ転送ごとにアドレスが増加するようなタイプで、一般的なメモリへの書き込みはこのタイプを使用します。

10は一定範囲でアドレスが循環するようなタイプで、キャッシュラインへの書き込みはこのタイプを使用します。

11は使用しません。

| バーストタイプ | AWBURST[1:0] | 説明 |

| Fixed | 00 | アドレス固定(同じアドレスに書き込み) |

| Increment | 01 | アドレス連続増加(通常のバースト書き込み) |

| Wrap | 10 | 一定範囲でアドレス循環(キャッシュメモリ向け) |

| Reserved | 11 | 使用不可(AXI4では未定義) |

AWSIZE

AWSIZEはバースト長を表します。0は1ワードのバースト転送、255は256ワードのバースト転送を表します。

AWLOCK

AWLOCKは通常のアクセスか排他的アクセスかを示す信号です。

| モード | AWLOCK | 説明 |

| Normal | 0 | 通常のトランザクション(ロックなし) |

| Atomic | 1 | 排他アクセス |

AWLOCK は マスター(CPUやDMAなど) から スレーブ(メモリやペリフェラル) に対して発行される制御信号の1つです。書き込みトランザクションに対して、ロックを要求するかどうかを示します。

具体例として、メモリへの排他アクセス時に使用されます。CPUやDMAがクリティカルセクションのデータを保護するために使用し、他のマスターが同じメモリアドレスにアクセスするのを防ぎます。他にも、組み込みシステムのマルチコア環境でのデータ整合性維持に有効です。

AWCACHE

AWCACHEは、キャッシュの動作方法を定義します。IPの仕様によりますが、基本的には、バッファ可能かそうでないか、キャッシュ可能かキャッシュ不可能かを定義します。

この信号を実際に使用することはほとんどありませんが、この信号が必須のタイプのメモリにアクセスする場合は、正しく設定する必要があります。

AWQOS

AWQOSは、AXI4バスの 書き込みトランザクションの優先度を示す信号 です。システム内の異なるトラフィッククラスに対して、サービス品質(QoS: Quality of Service)を管理するために使用されます。

- AXIマスター(CPU, DMA, FPGA など)が書き込みトランザクションにQoS情報を付与

- AXIスレーブ(メモリコントローラ, バススイッチなど)がこの値を使用し、優先度を調整

- システム全体のトラフィック管理 を行い、重要なデータ転送をスムーズに実行できるようにする

例えば次のように設定されます。AWQOSは4ビットの信号で、値が大きいほど優先度が高いことにします。

| 優先度 | AWQOS[3:0] | 用途例 |

| 低 | 0000 | バックグラウンドトラフィック(低優先度データ転送) |

| 中 | 0100 | 一般的なデータ転送(標準メモリアクセス) |

| 高 | 1000 | リアルタイム処理(オーディオ, 映像データ, 低遅延処理) |

| 最高 | 1111 | 緊急トラフィック(システム制御, クリティカルデータ) |

ただし、実際の優先度の決定方法はシステム(バスインターコネクト、スイッチ、メモリコントローラ)によることに注意してください。

AWUSER

AWUSERはユーザ定義の信号です。トランザクションのラベルなど、必要な用途で使用できます。

AWPROT

AWPROTはアクセス保護を定義します。

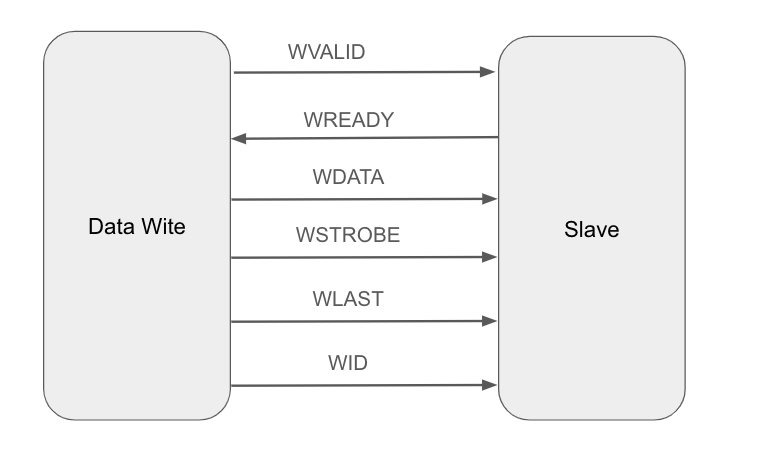

書き込み用データバス

| 信号名 | ソース | 説明 |

| WVALID | Master | マスターから送信されるデータが有効であることを示す |

| WREADY | Slave | 受信側が受信可能状態であることを示す |

| WDATA | Master | 書き込みデータ 最大128バイトのデータバス |

| WSTROBE | Master | 各バイトの有効性を示す |

| WLAST | Master | トランザクションの最後のデータワードであることを示す |

| WID | Master | トランザクションID |

WVALID

マスターから送信されるデータが有効であることを示す信号線です。

WREADY

スレーブが受信可能状態であることを示す信号線です。

WDATA

WDATAは書き込みデータです。最大で128バイト幅のデータバスになります。

WSTROBE

データバスの各バイトの有効性を識別する信号線です

WLAST

書き込むデータワードの最後のワードを示す信号線です。この信号線がアサートされるとバースト転送において、最後のデータを示します。

WID

データのトランザクションIDを示します。

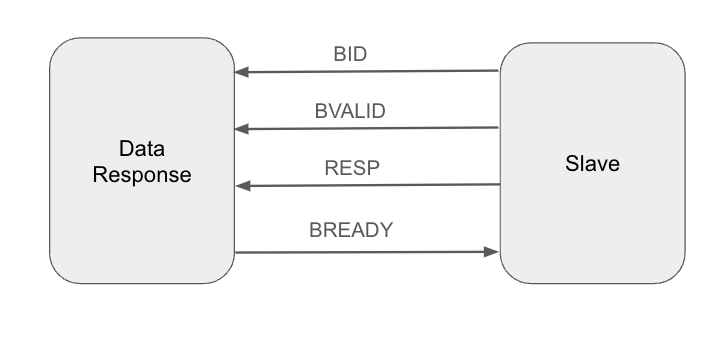

書き込み応答用バス

| 信号名 | ソース | 説明 |

| BID | Slave | トランザクションID |

| BVALID | Slave | 書き込み応答が有効であることを示す |

| BREADY | Master | 受信可能状態であることを示す |

| BRESP | Slave | スレーブからの応答情報 |

| Response | BRESP[1:0] | 説明 |

| OKAY | 00 | 書き込みが成功 |

| EXOKAY | 01 | 排他アクセスが問題なし |

| SLVERR | 10 | スレーブの範囲内のアドレスが指定されているがエラー |

| DECERR | 11 | スレーブの範囲外のアドレスが指定されていてエラー |

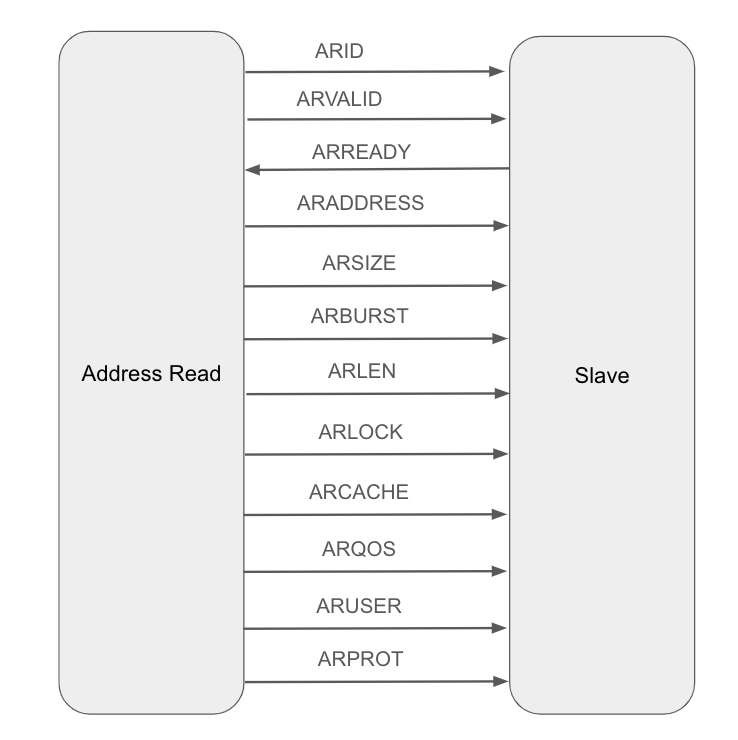

読み出しアドレス用バス

| 信号名 | ソース | 説明 |

| ARVALID | Master | 読み出しアドレスが有効であることを示す |

| ARREADY | Slave | スレーブが受信可能状態であることを示す |

| ARADDRESS | Master | 読み出しアドレス バースト転送のベースアドレスとなる |

| ARLEN | Master | バースト長 0 = 1, 255=最大で256 |

| ARSIZE | Master | バイトサブセット 2^AWSIZE, 0=1バイト, 7=128バイト |

| ARBURST | Master | バーストタイプ 0 = Fixed 1 = Increment 2 = Wrap 3 = Reserved |

| ARLOCK | Master | アトミックアクセス 0 = ノーマルアクセス 1 = 排他的アクセス |

| ARCACHE | Master | メモリタイプ, バッファ可能, バッファ不可、キャッシュ可能、キャッシュ不可 などを表す信号 |

| ARPOT | Master | アクセス保護, 3ビット幅 1ビット目 1 = 特権アクセス 0 = 非特権アクセス 2ビット目 1 = セキュアアクセス 0 = 非セキュアアクセス 3ビット目 1 = 命令 0 = データ |

| ARQOS | Master | ユーザ定義のQOS(Quality of Service)の値 トランザクションのラベル |

| ARUSER | Master | ユーザ定義 |

| ARID | Master | トランザクションID |

各信号の用途については、書き込みと同様です。

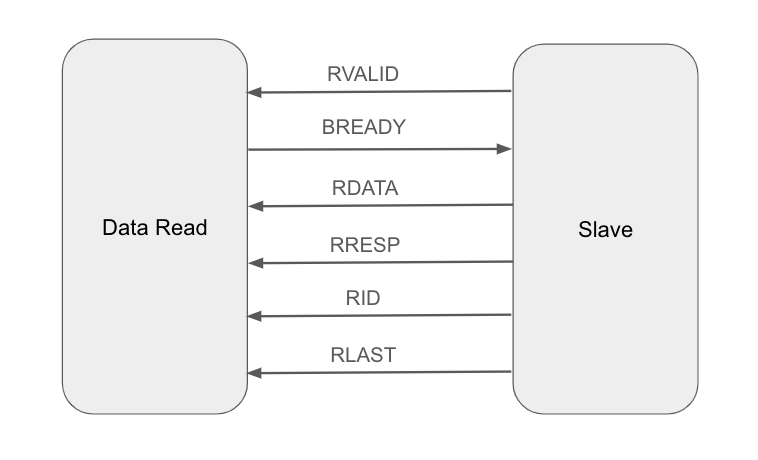

読み出しデータ用バス

| 信号名 | ソース | 説明 |

| RVALID | Slave | 読み出しデータが有効であることを示す |

| RREADY | Master | 受信側が受信可能状態であることを示す |

| RDATA | Slave | 読み出しデータ 最大128バイトのデータバス |

| RRESP | Slave | 応答情報 |

| RID | Slave | トランザクションID |

| RLAST | Slave | バースト転送の最後のワードを示す |

| Response | RRESEP[1:0] | 説明 |

| OKAY | 00 | 読み出しが成功 |

| EXOKAY | 01 | 排他アクセスが問題なし |

| SLVERR | 10 | スレーブの範囲内のアドレスが指定されているがエラー |

| DECERR | 11 | スレーブの範囲外のアドレスが指定されていてエラー |

トランザクション

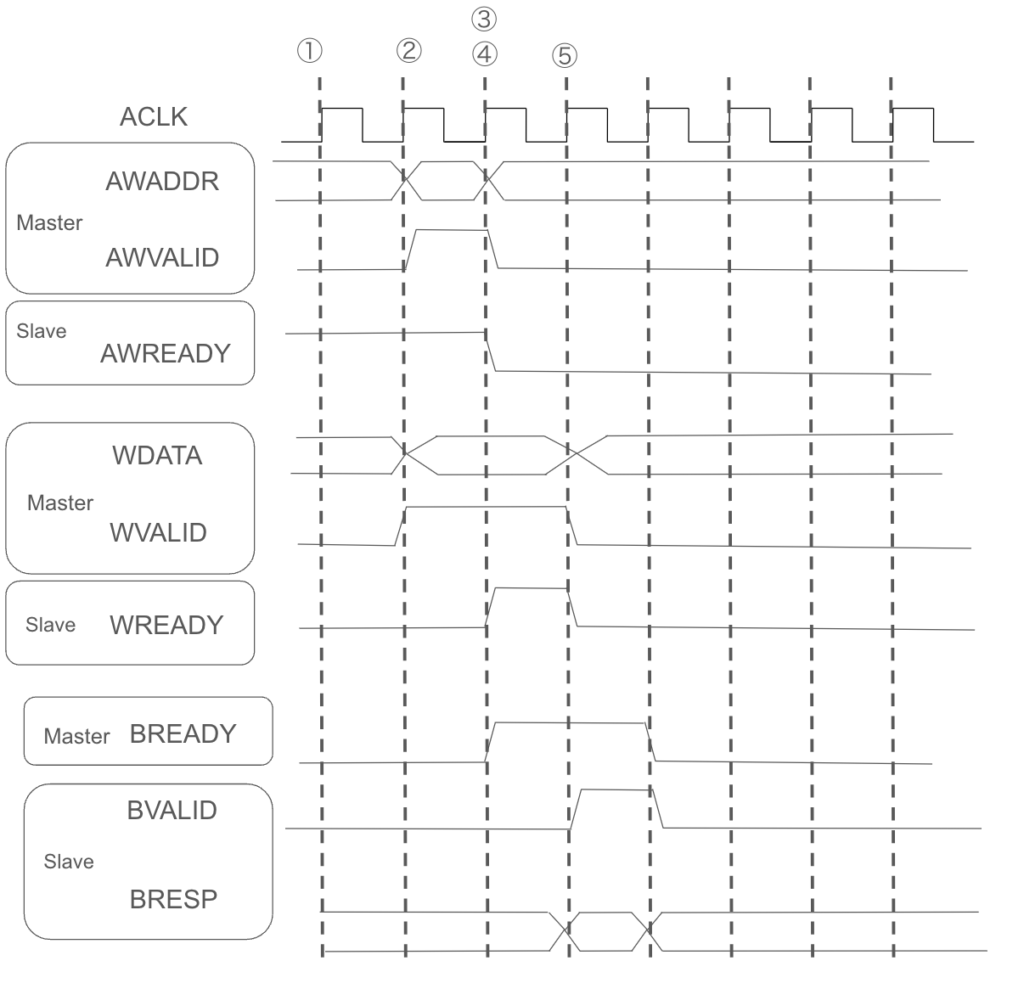

書き込みトランザクションのタイミングチャート

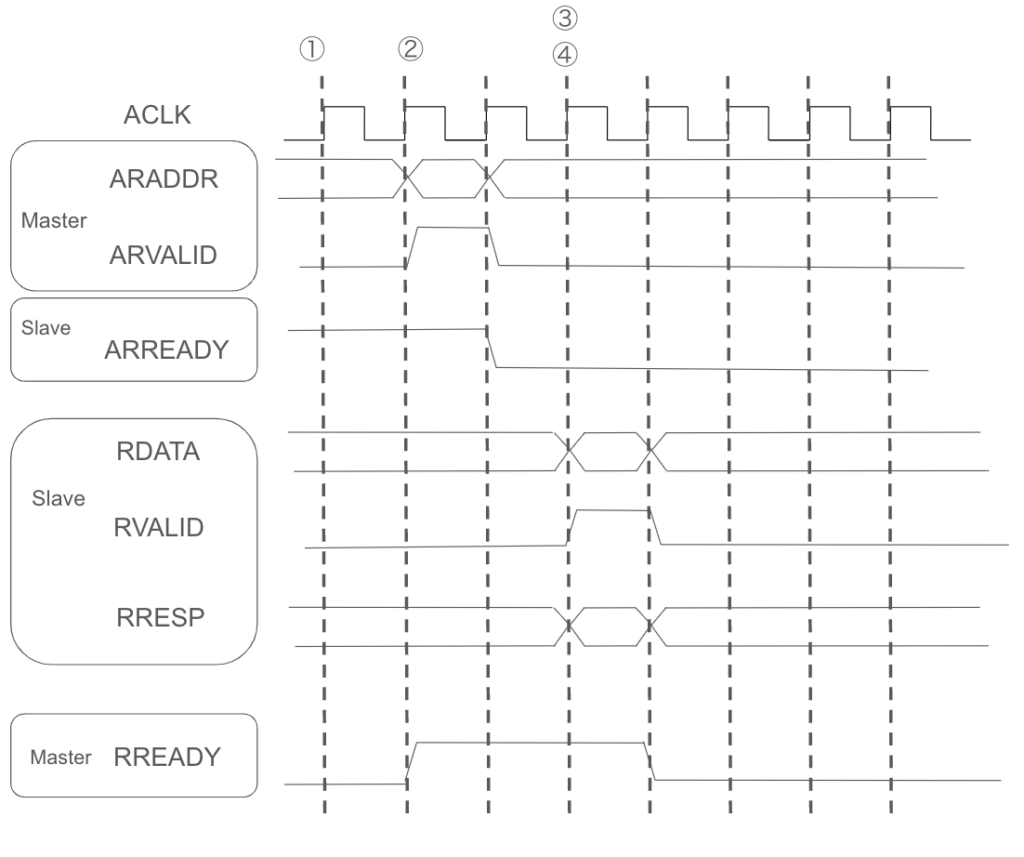

読み出しトランザクションのタイミングチャート

まとめ

本記事では、AXI4について解説しました。AXI4-Liteとの比較をし、各信号バスがどのような役割で使用されているかを詳しく見ました。また、タイミングチャートを使って、典型的なトランザクションを確認しました。

コメント