ハードウェアの作成

事前設定

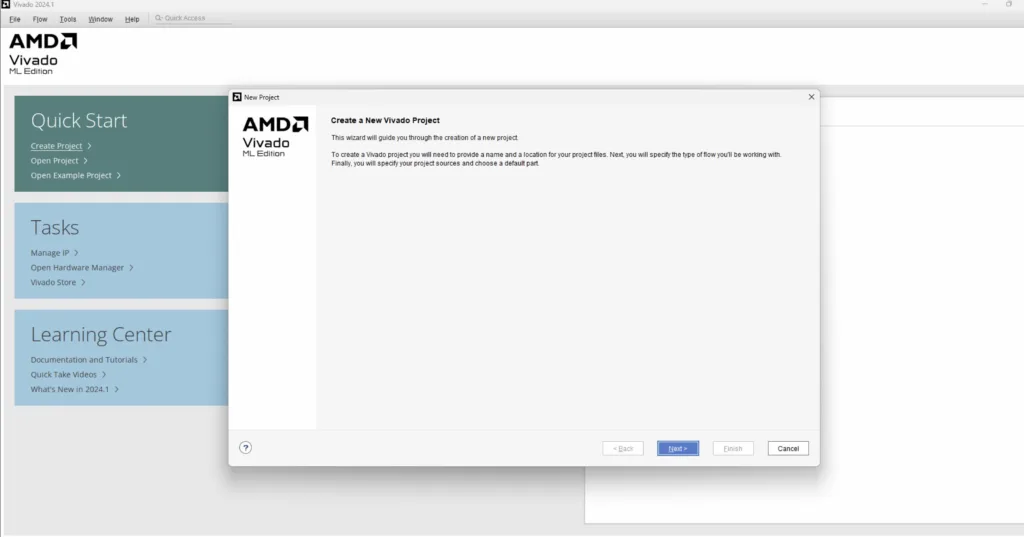

Vivadoを起動し、Create Projectを選択すると、以下のような画面が開きます。Nextとすると

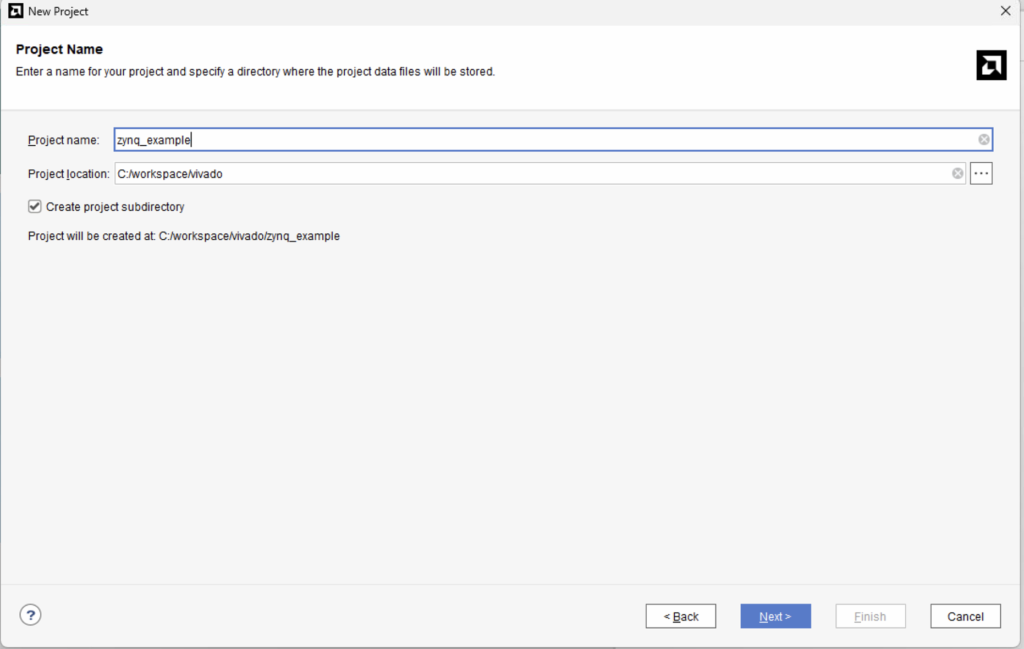

プロジェクト設定画面が出るので、

Project name: zynq_example(任意のプロジェクト名)

Project location: C:/workspace/vivado(プロジェクトの場所)

を設定し、Nextを押す。

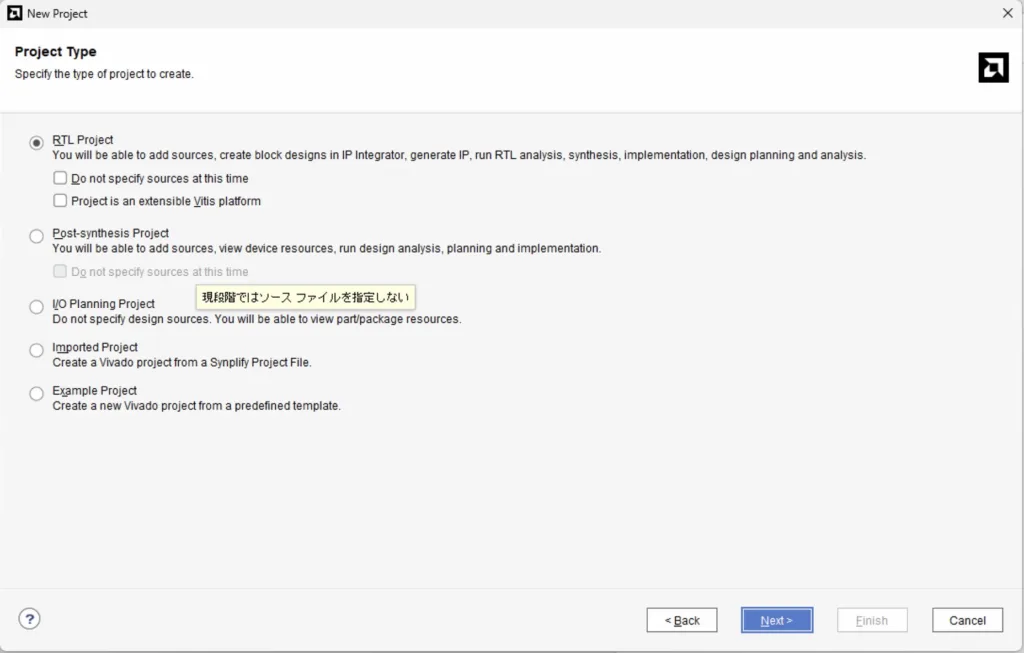

Project typeの設定があるので、RTL Projectを選択し、Nextを押す。

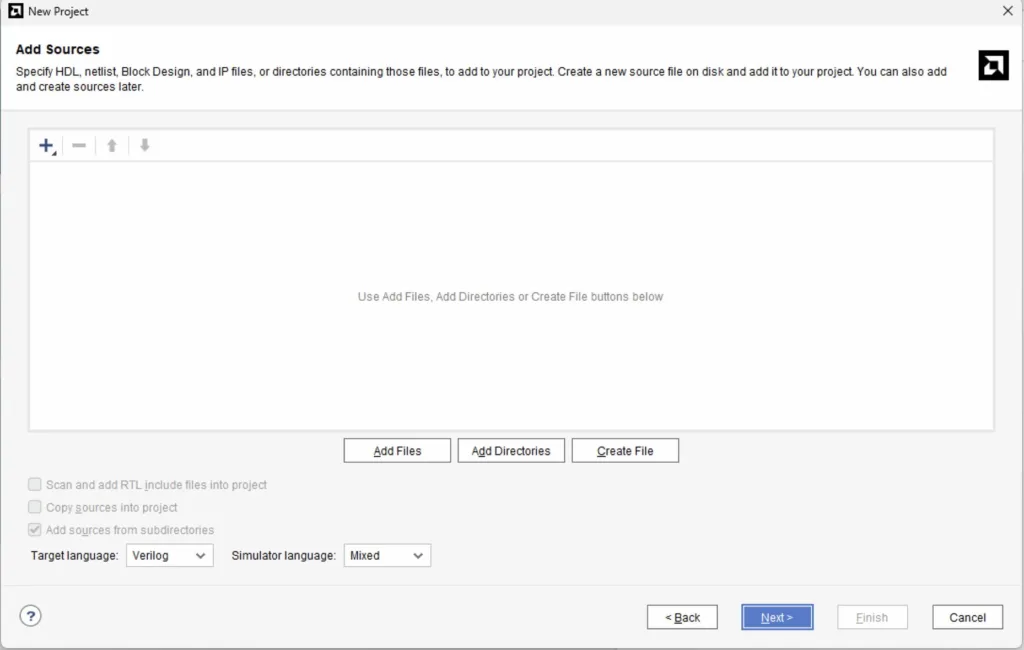

Add SourcesはそのままNextを押す。

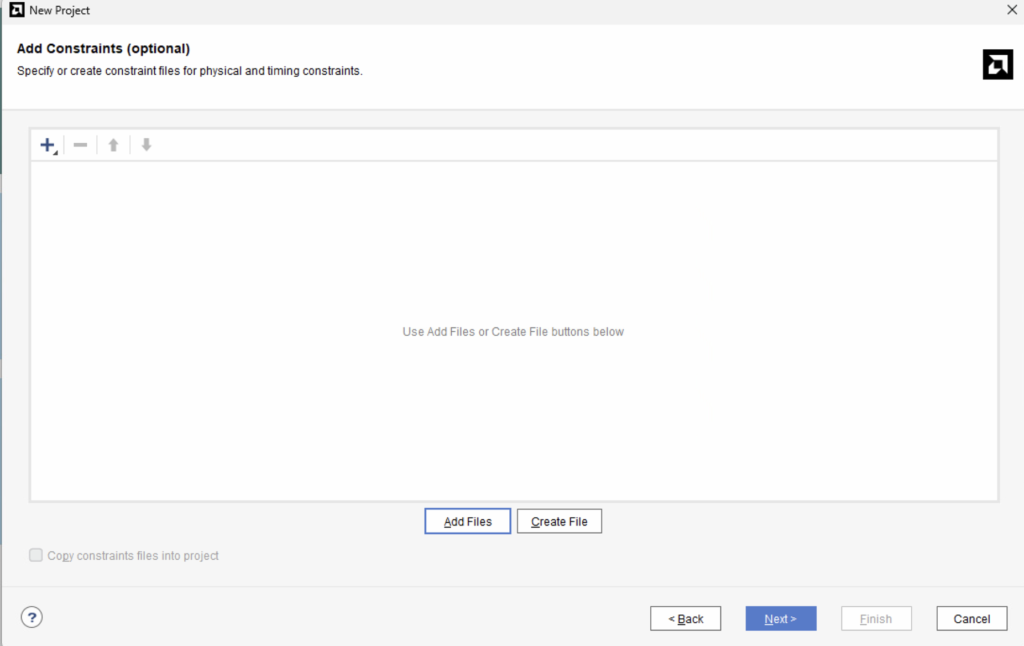

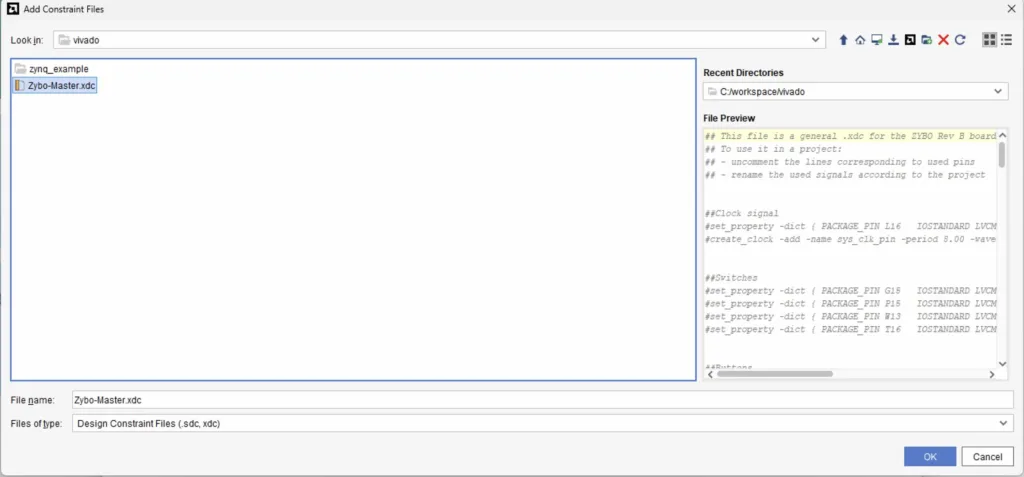

Add Constraintsでは、Zyboの制約ファイルを使用したいので、Digilentのgithubからダウンロードしておく。Add Filesからダウンロードした、制約ファイルを選択する。

制約ファイルはZybo-Master.xdcとなっているので、これを使用する。選択、OKを押す。

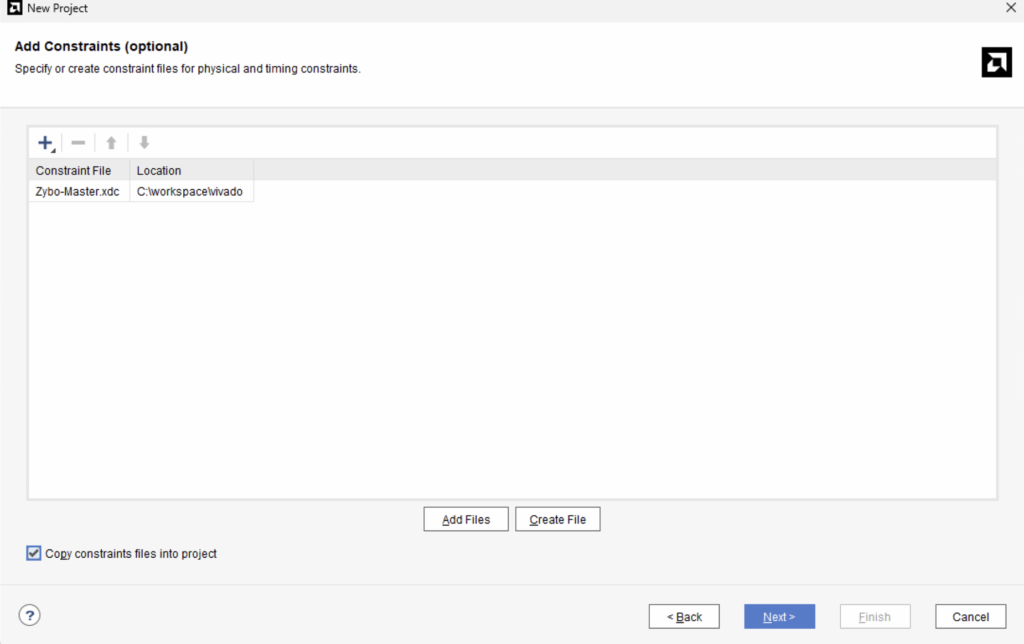

すると、以下のように読み込まれていることが確認できる。Copy constraints files into projectはチェックしておく。こうすることで、プロジェクトごとに制約ファイルがコピーされるので、こちらをおすすめします。その後、Nextを選択します。

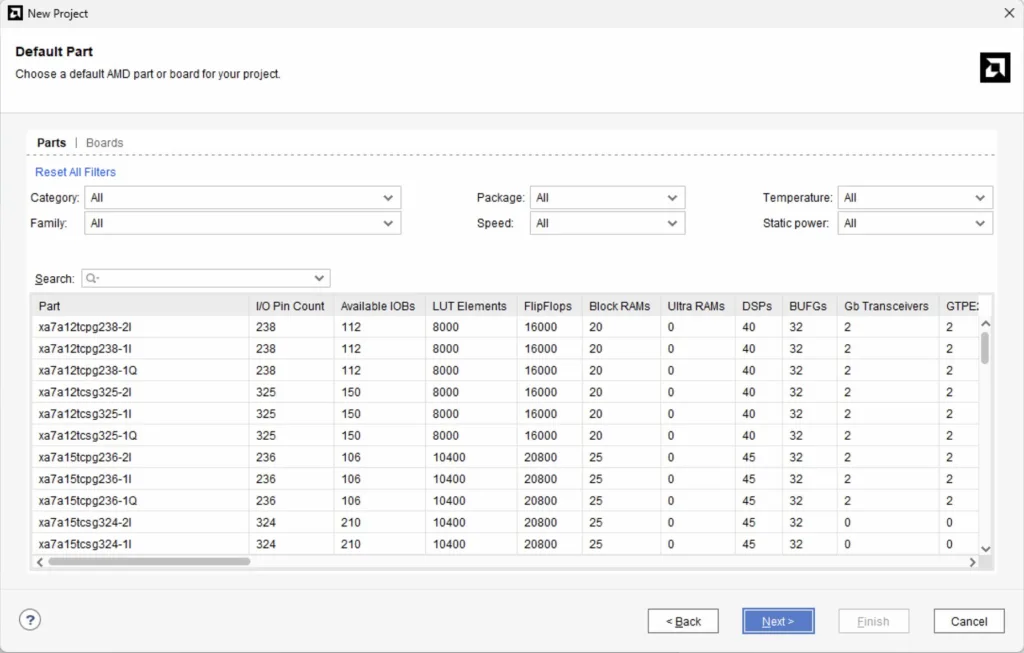

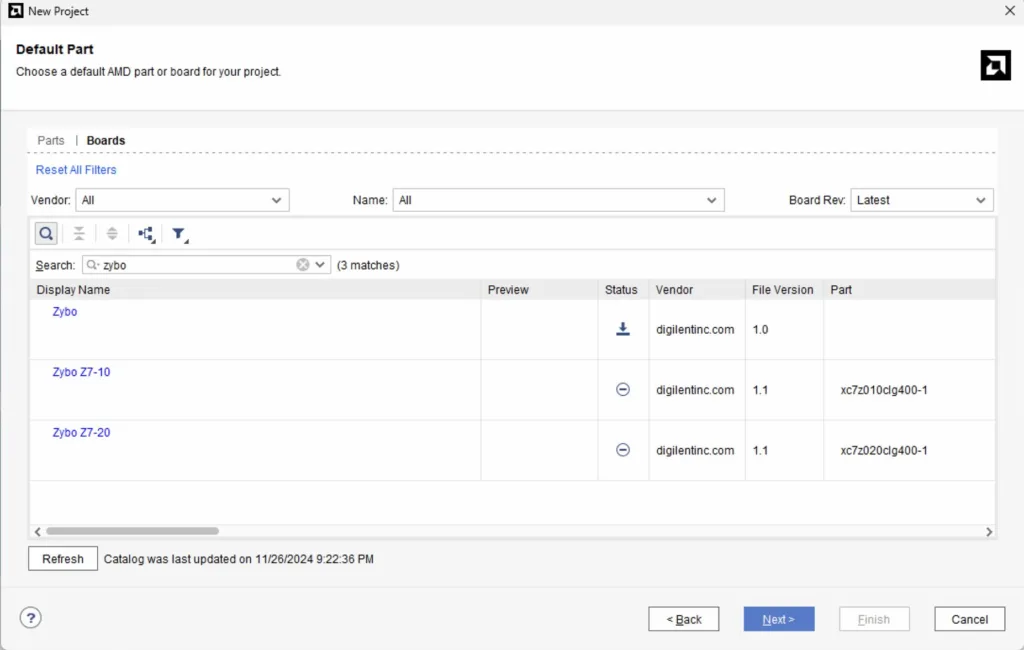

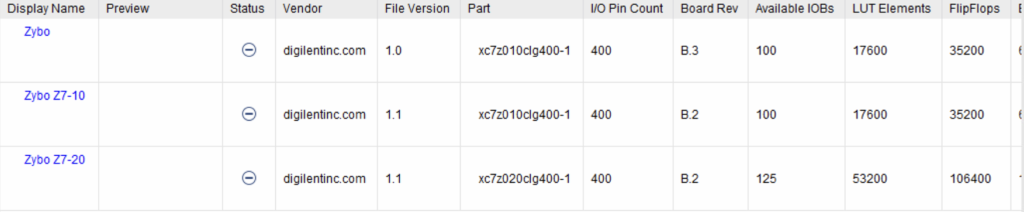

次に、partを選択する画面に遷移するので、実装対象のボードを選択します。まずは、Boardsを選択して、ボード選択画面に遷移します。

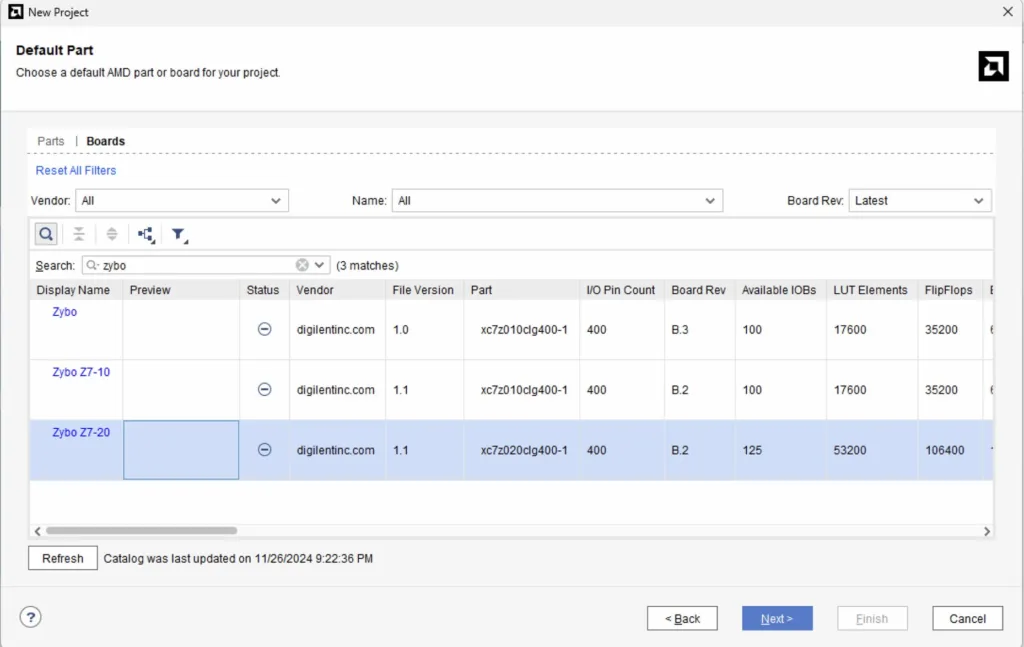

その後、Searchから以下のようにZyboと検索すると、Zybo関連のボードが表示されるので、ボードを選択します。今回は、Zybo Z7-20を選択します。Zybo Z7-20を使用している方はそちらを選択してください。

また、Statusが矢印のマークになっている場合は、そのボードに関する情報がインストールされていないので、Installしてください。Installは矢印のマークをクリックするとインストールされます。

インストールされると、例えば今回だとZyboのStatusを見ると変化しています。Zybo Z7-10, Zybo Z7-20はインストール済みだったので、変化していません。

Zybo Z7-20を選択して、Nextを押します。

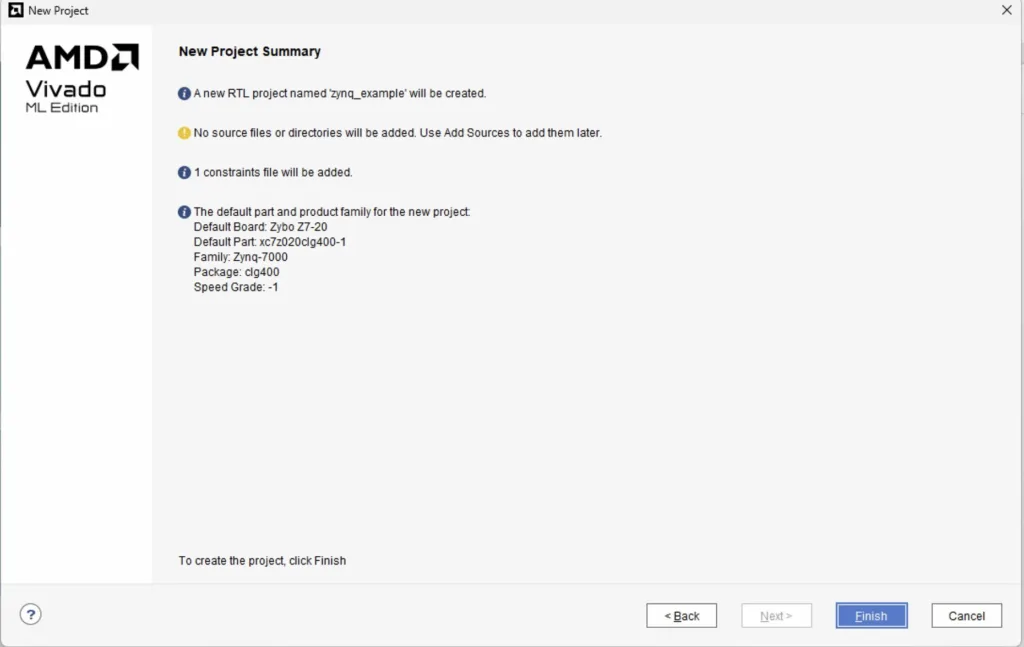

最後にFinishを押して完了です。

ハードウェアデザインの作成

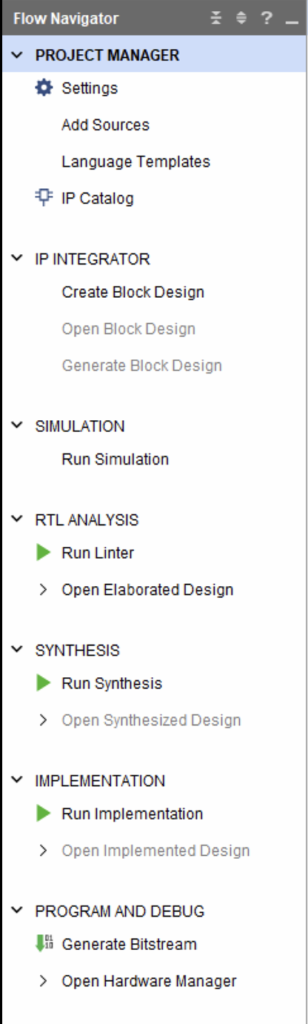

Create Block Designを選択します。

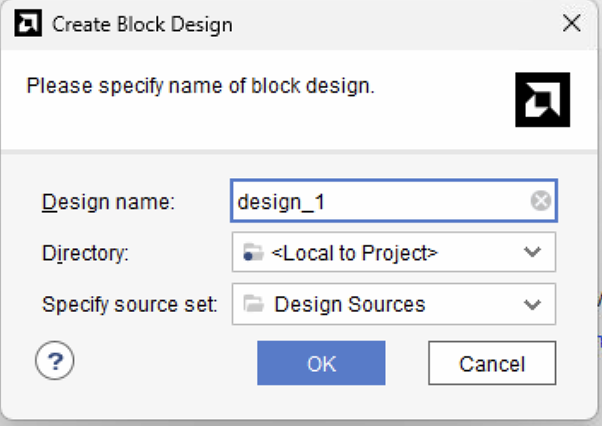

Design nameを入力して、OKを押します。

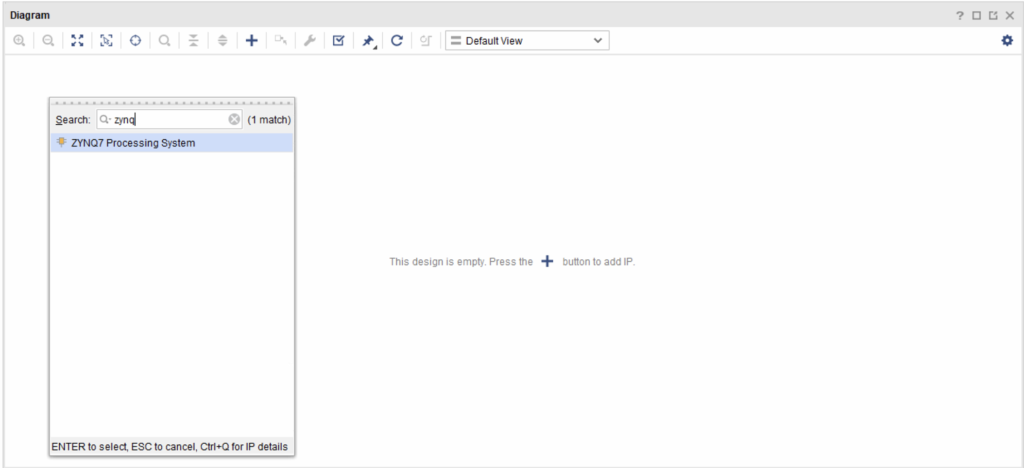

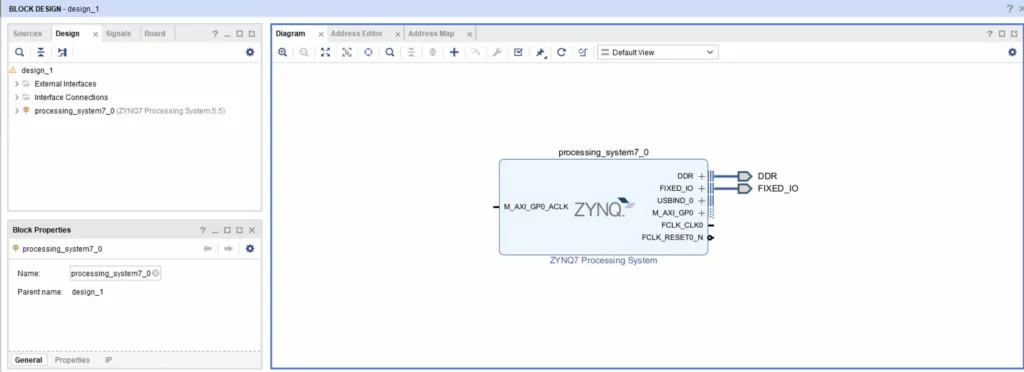

Diagram画面から、+マークを押すと、IPの検索画面が出るので、zynqと入力します。ZYNQ7 Processin Systemがあるので、選択します。

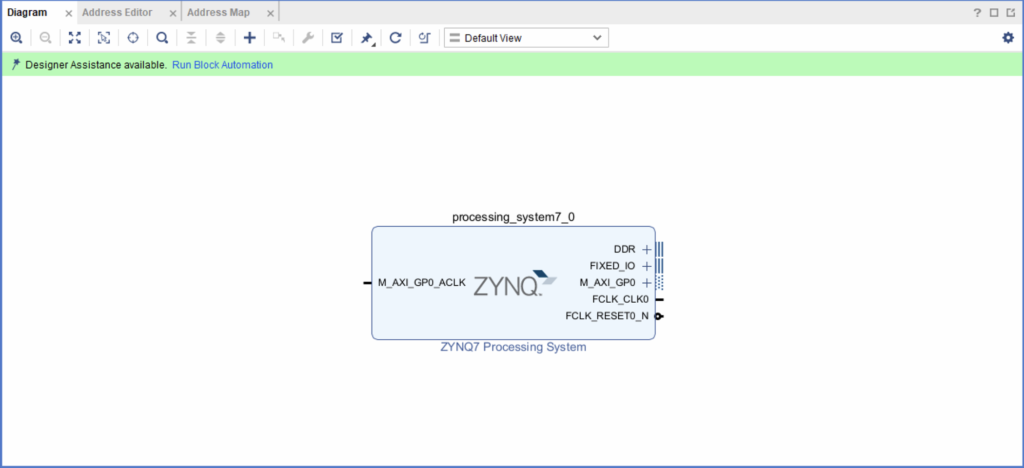

選択すると、以下のようにDiagram上にZYNQが配置されたことがわかります。Run Block Automationを押します。

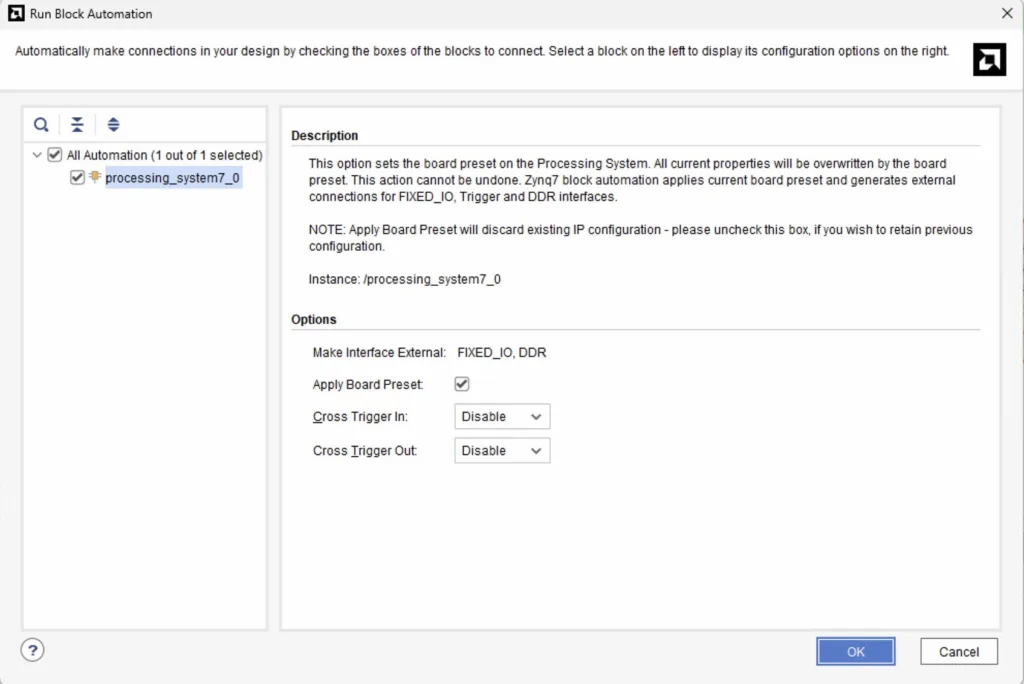

すると以下のような画面に遷移するので、OKを押します。

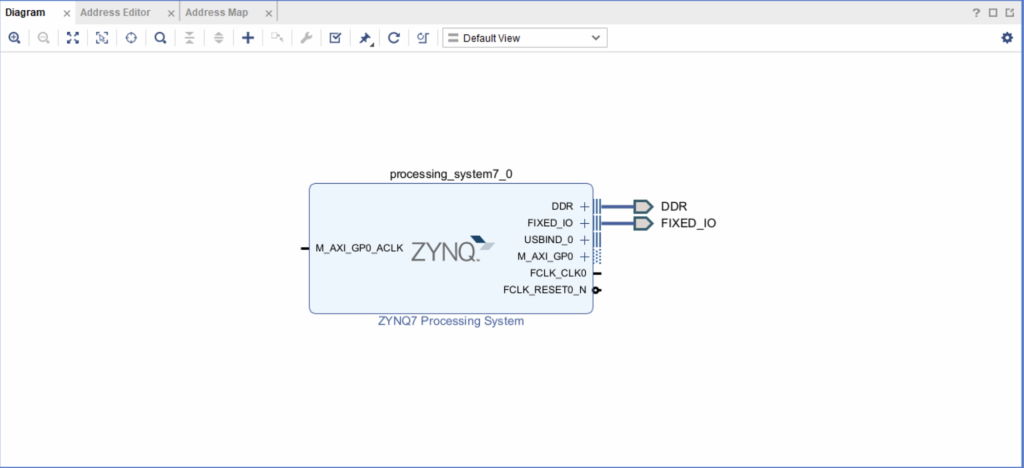

以下のように配置されます。

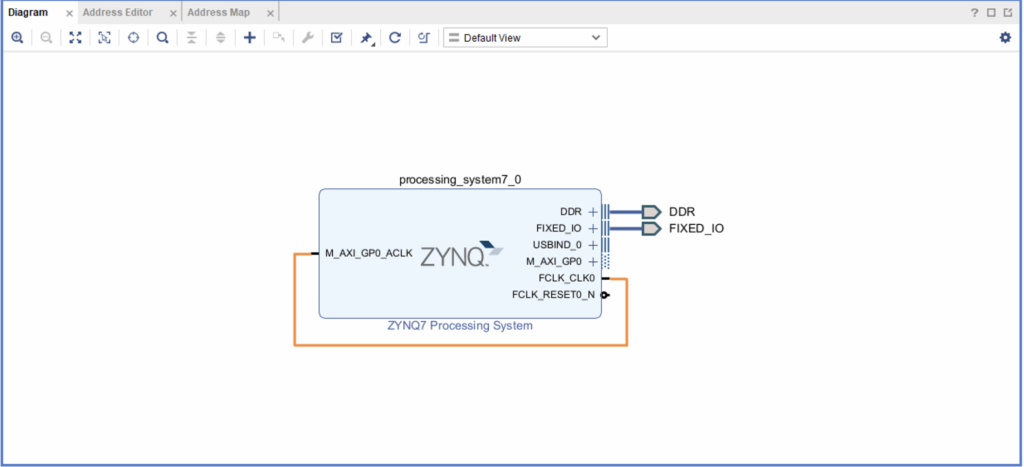

FCLK_CLK0をM_AXI_GP0_ACLKを繋げます。FCLK_CLK0のピンを左クリックしならがM_AXI_GP0_ACLKにカーソルを移動させると以下のように接続することができます。これで、ハードウェア側の設定は完了です。

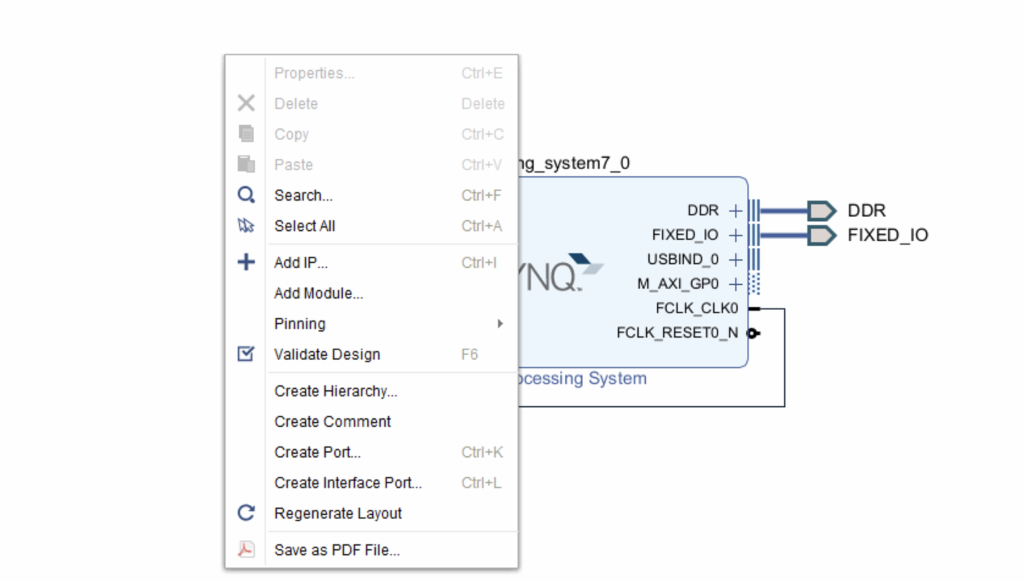

最後にDiagram上で、右クリックして、Validate Designを実行します。

ハードウェアデザインの実装

DesignからSourceタブに変更します。

design_1を右クリックし、Create HDL Wrapperを選択します。

以下のような画面がポップアップされるので、OKで完了です。

実装

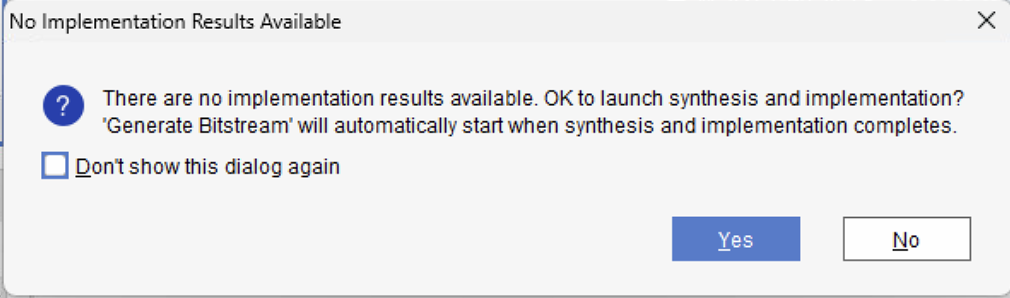

次にGenerate BitstreamでFPGAに読み込ませるハードウェアデザインファイルを生成します。以下のようなポップアップが出ることがありますが、OKで問題ありません。

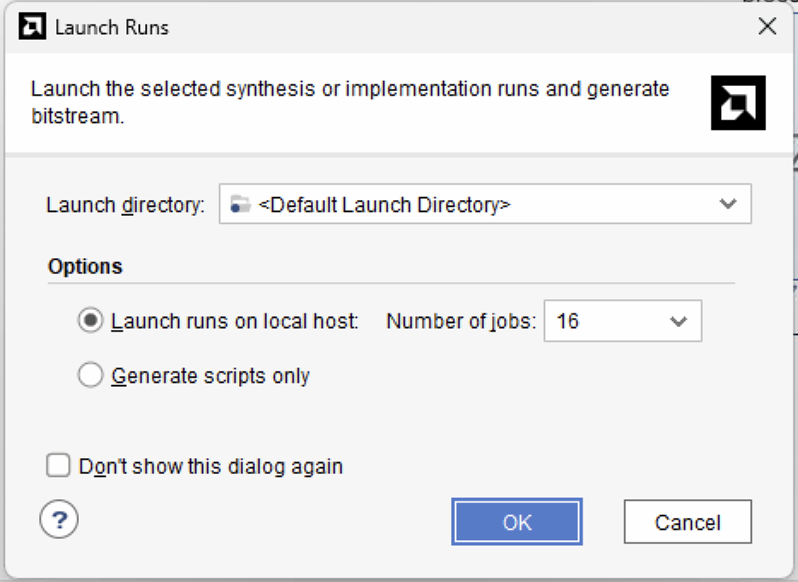

ここも、OKで問題ありません。

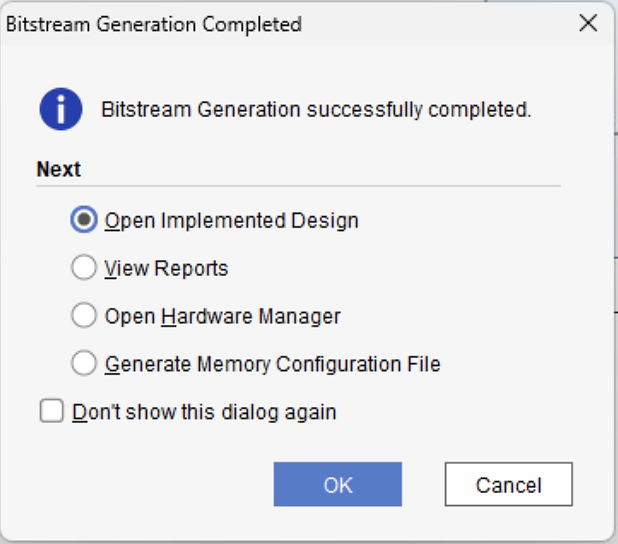

以下のように、Bitstream Generation Completedとなれば完了になります。Cancelでポップアップを消去します。

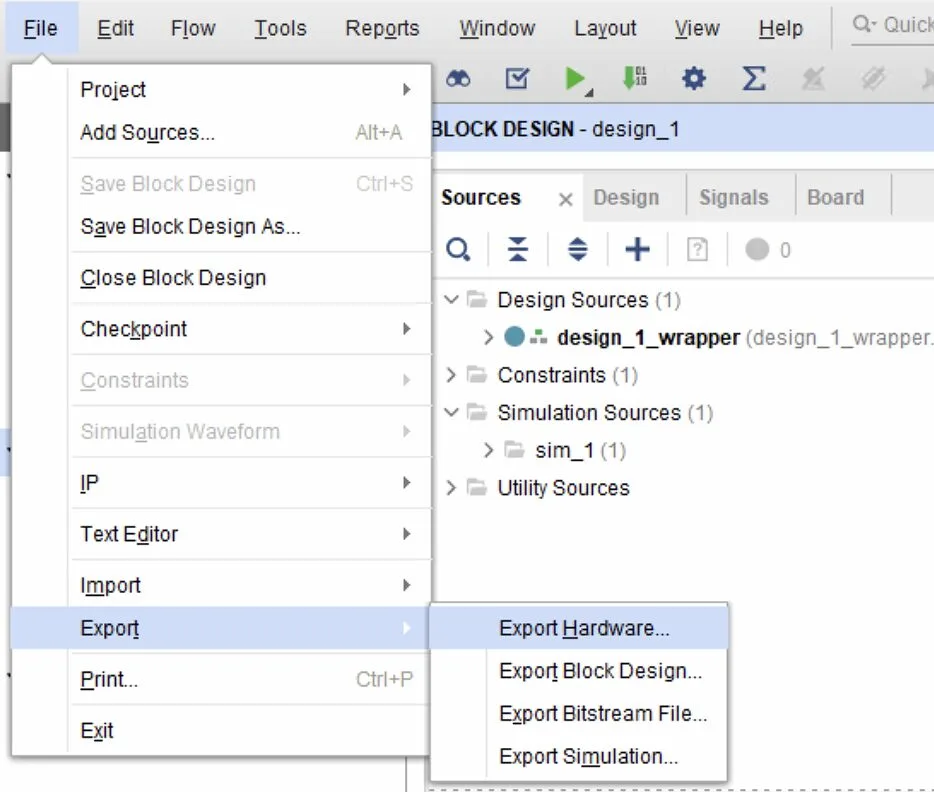

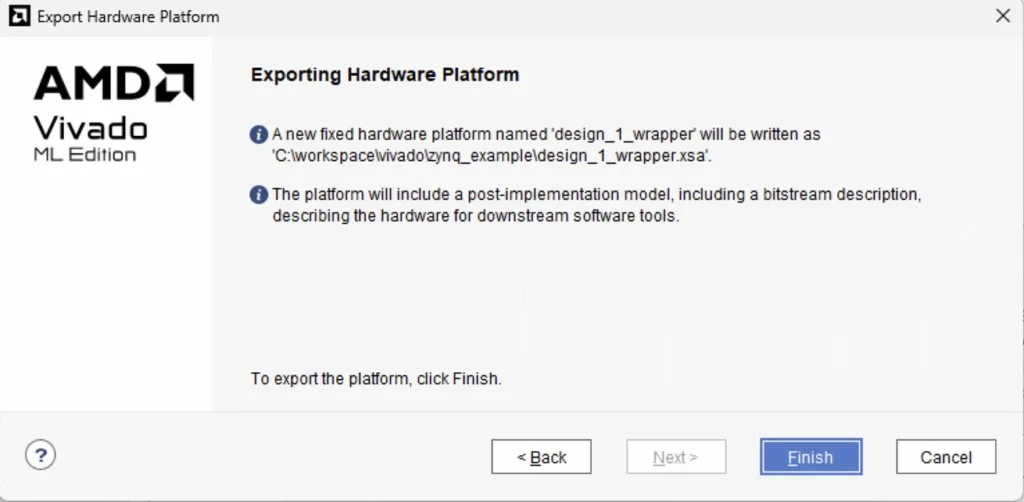

File -> Export -> Export Hardwareを選択して、

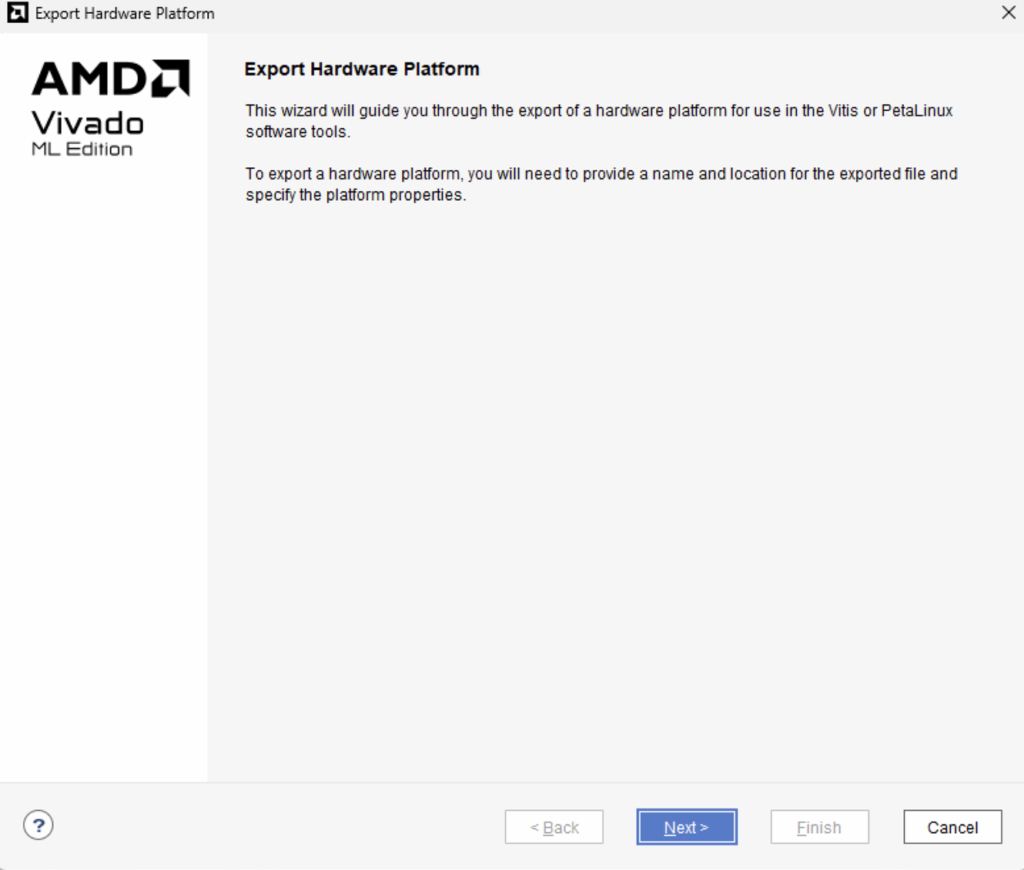

Nextで次の画面にします。

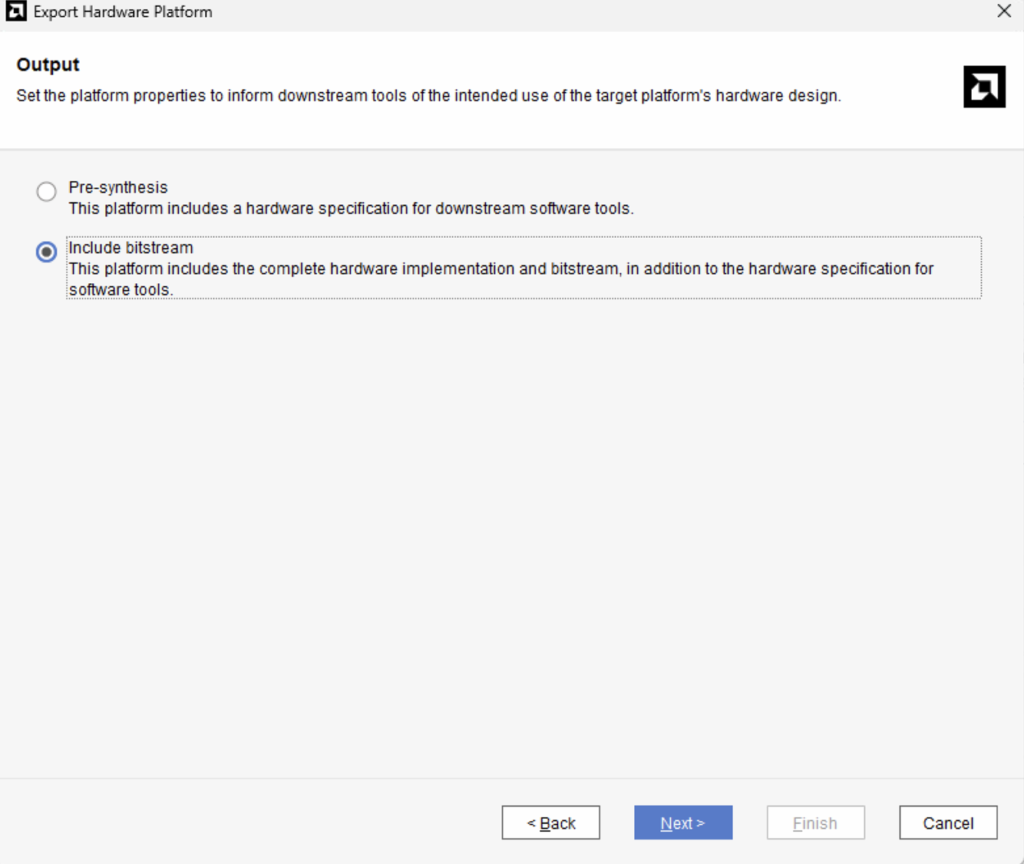

Include bitstreamを選択します。

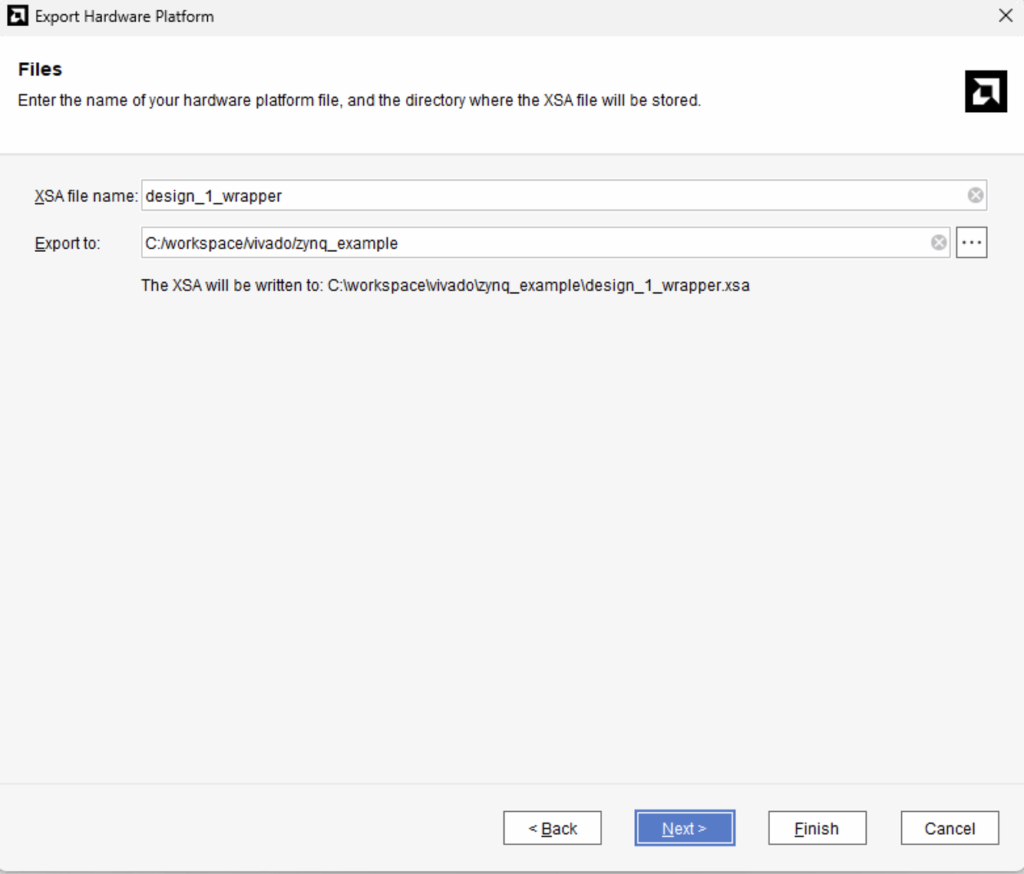

xsaファイルとその出力場所を指定します。今回はこのままデフォルトの位置を使用します。Nextを押して、

Finishで完了になります。

ソフトウェアの作成

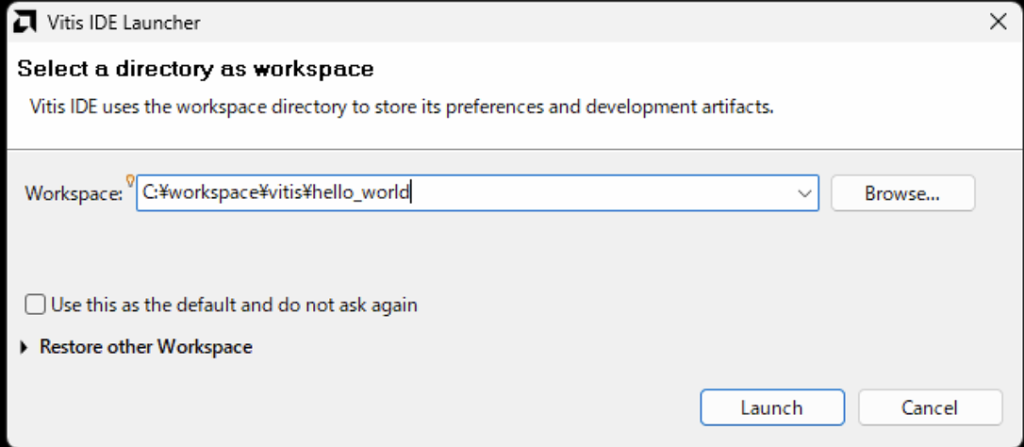

Vitis Classicを起動します。起動すると、ワークスペースとするディレクトリの設定します。ここでは、以下のような設定にています。Launchでソフトウェアを起動します。

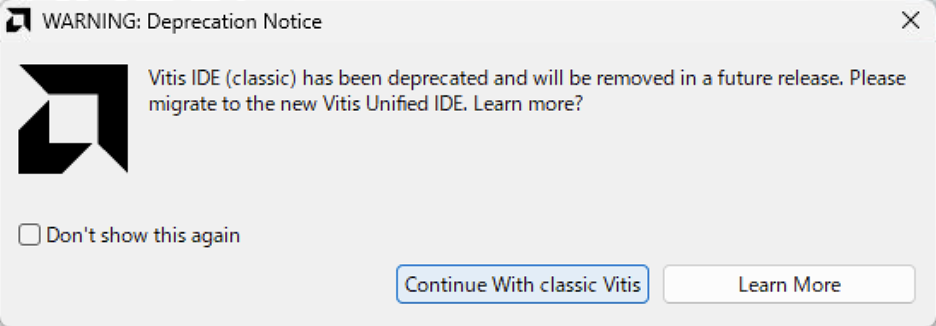

Continue with classic vitisを選択します。

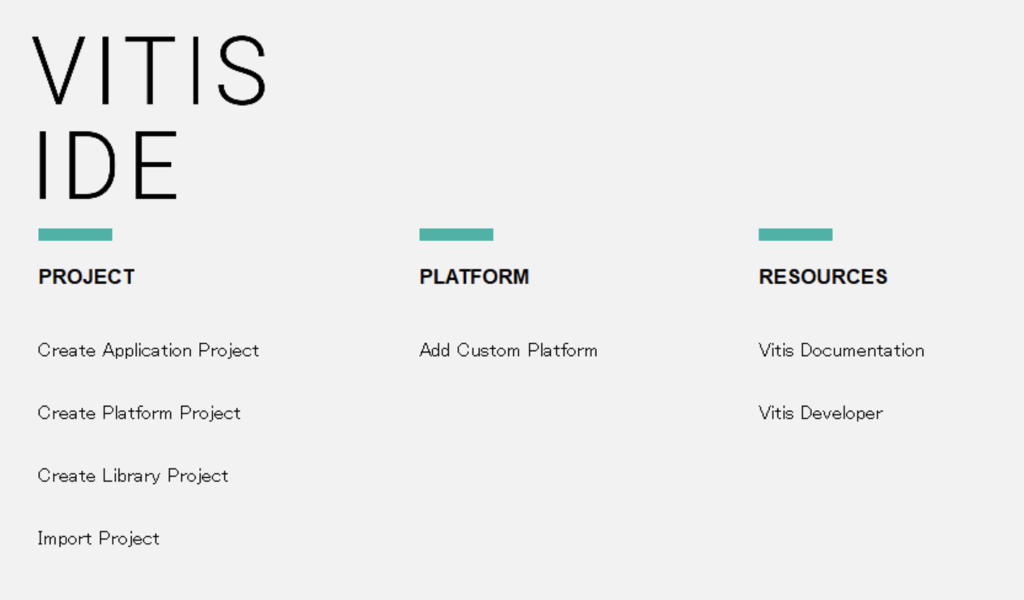

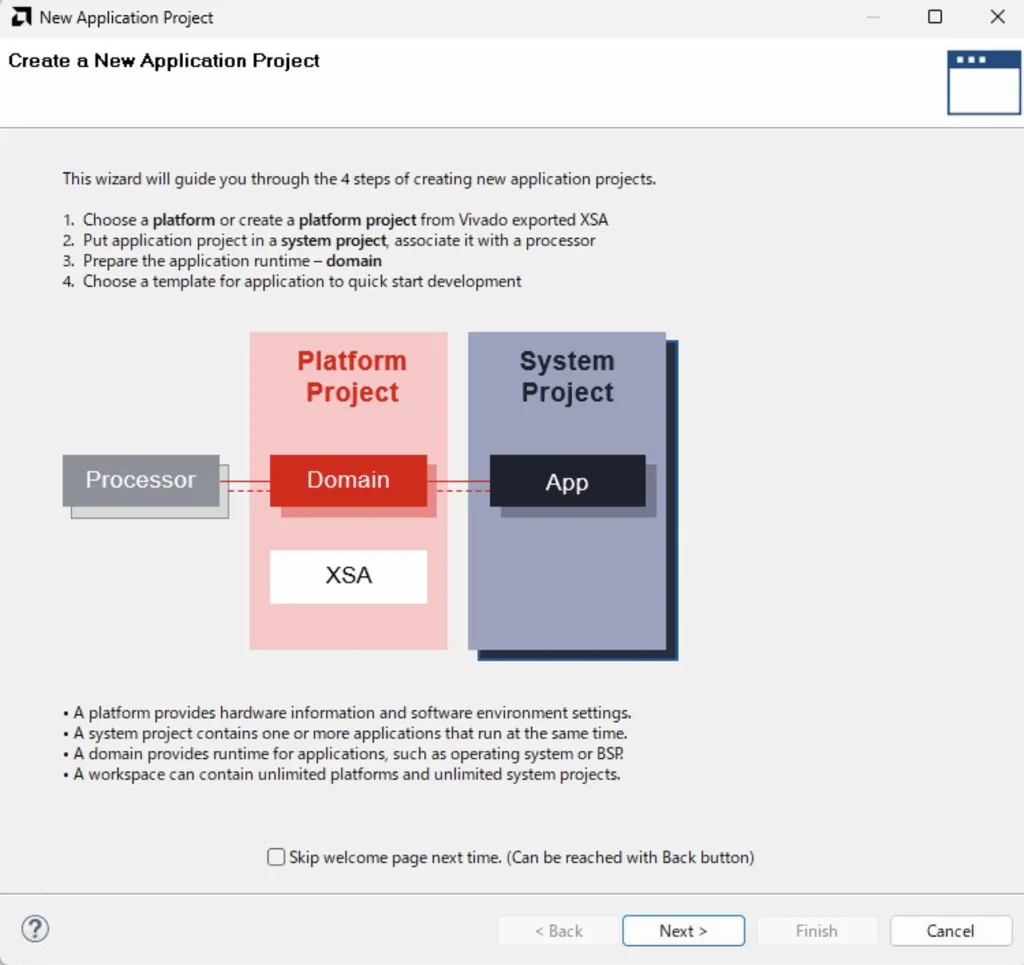

まずは、Create Application ProjectからApplicationプロジェクトを作成します。

ここでは、Nextを押すと次の画面に遷移します。

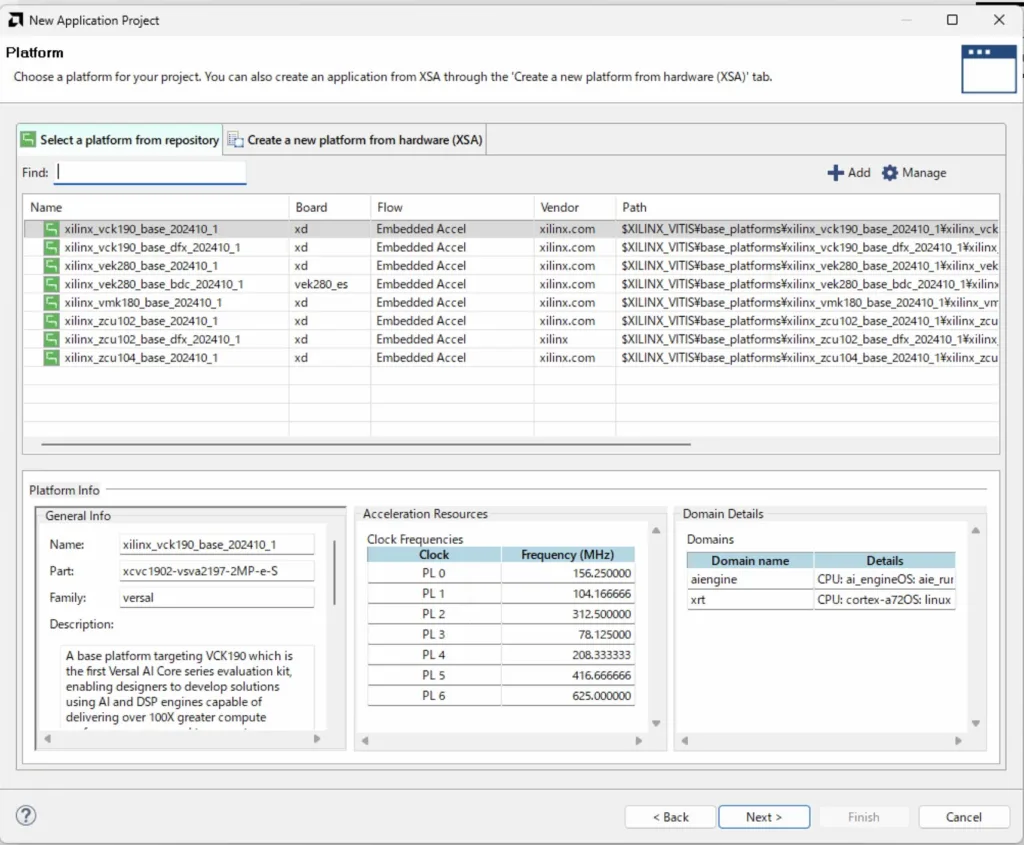

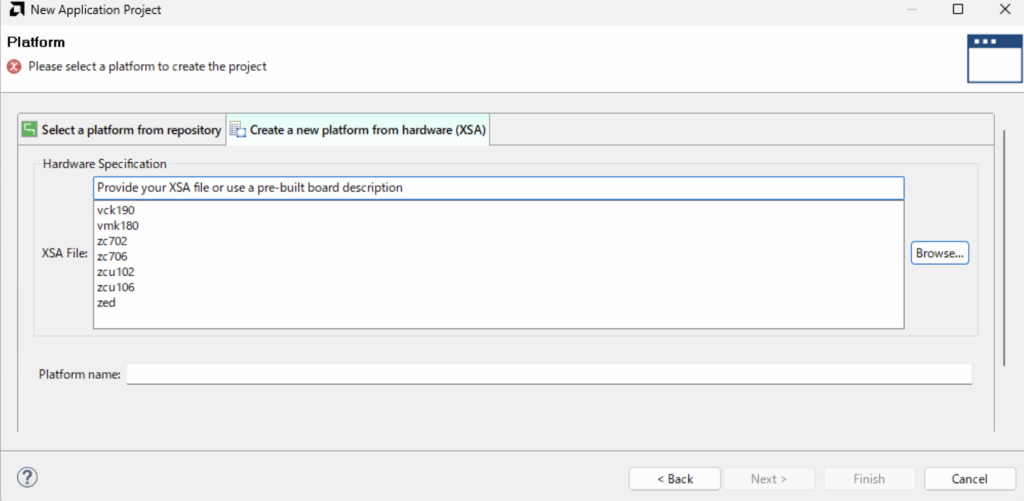

以下のような画面に遷移になるので、Create a new platform rom hardware(XSA)に切り替えます。

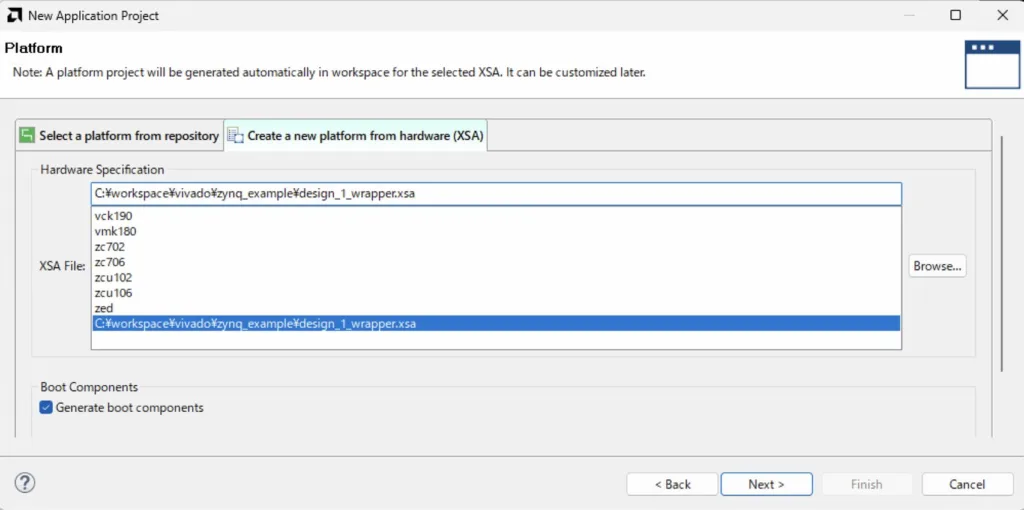

Browseから先ほど作成したxsaファイルを選択します。(ここでは、design_1_wrapper.xsa)

すると、以下のようになりますので、Nextを押します。

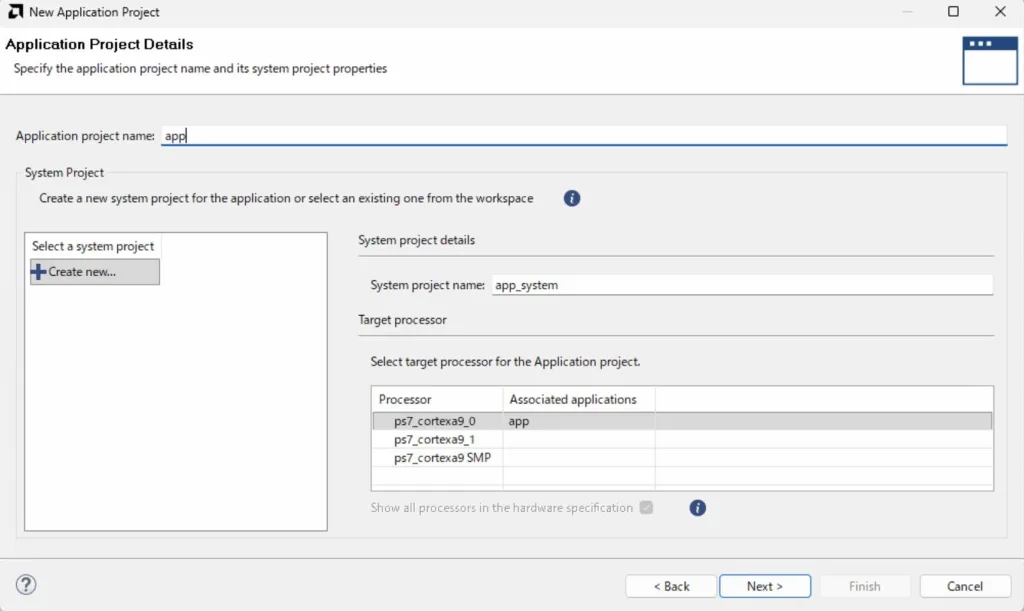

以下のようにApplication projectの名前を入力する画面になるので、任意の名前を入力します。ここでは、appと入力しています。Nextとします。

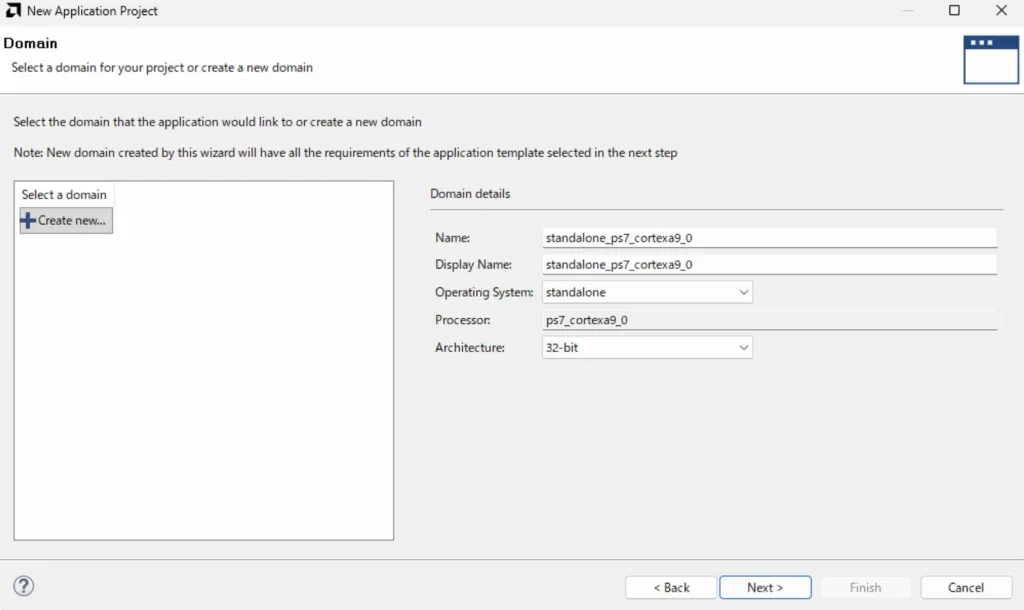

以下のような画面に遷移するので、さらにNextとします。

application projectのtemplateの選択ができる画面に遷移するので、Hello Woldを選択してFinishします。

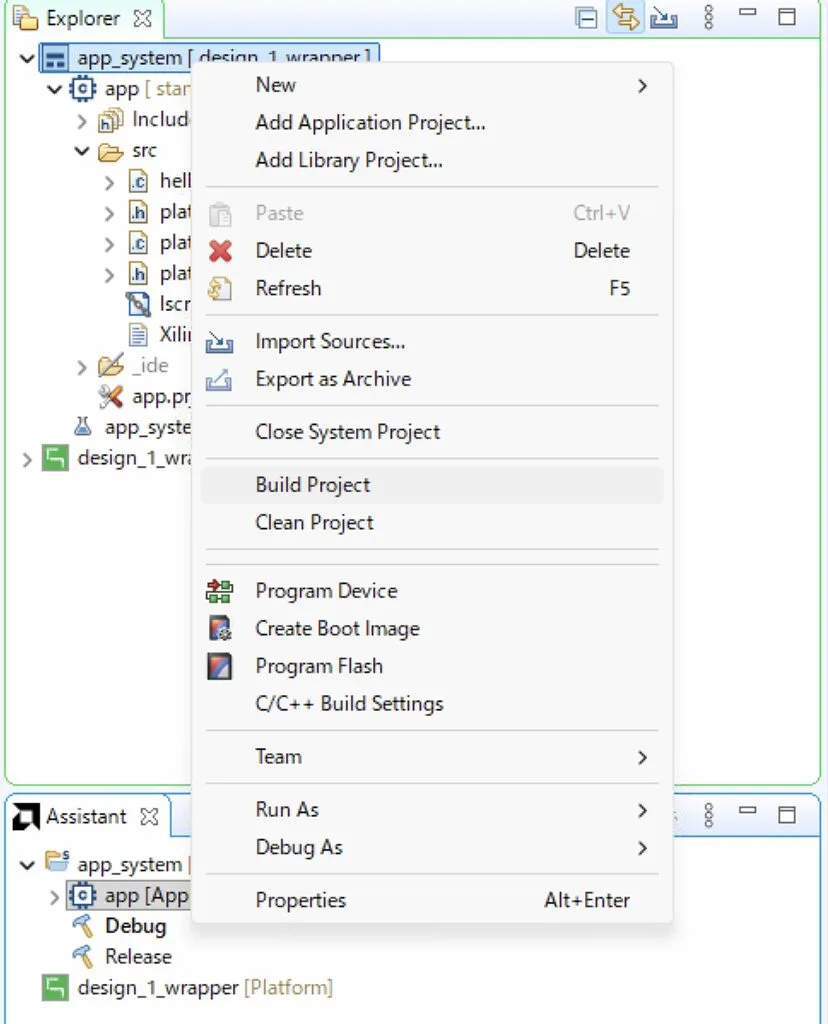

app_systemを選択した上で、右クリックすると以下のようになるのでBuild Projectでアプリケーションをビルドします。

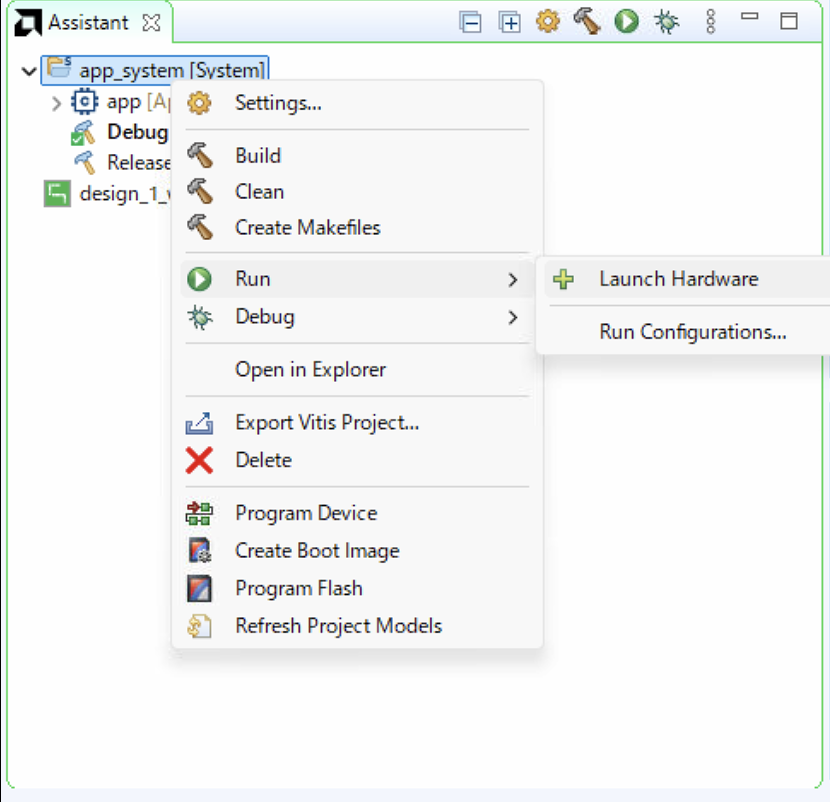

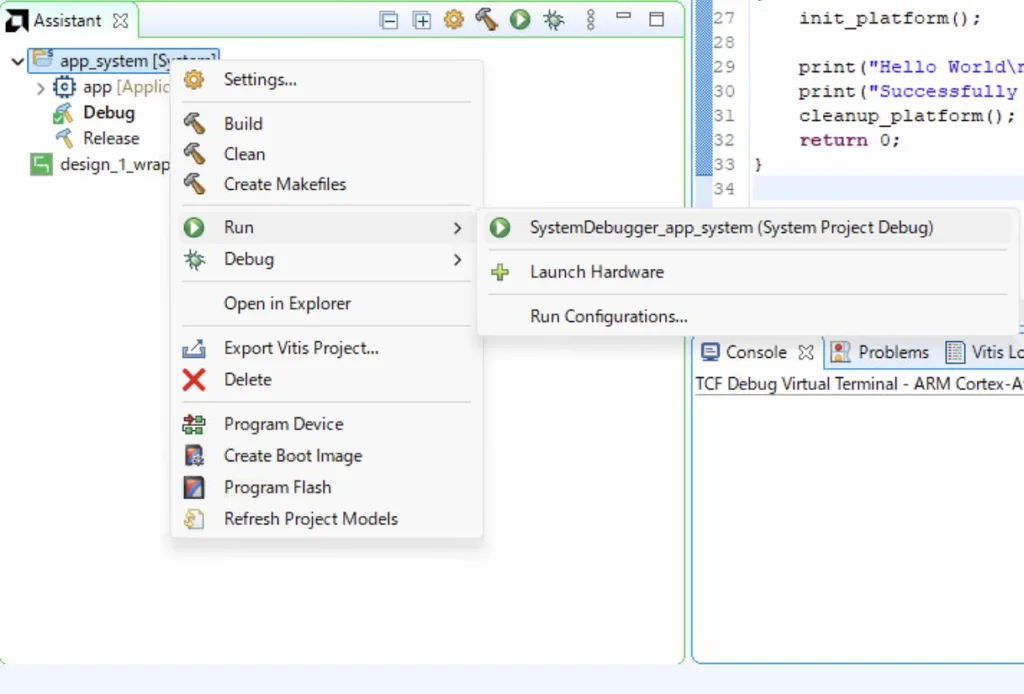

Assistantからapp_systemを選択した状態で、右クリックすると以下の画面のようになるので、Launch Hardwareを選択します。この時点でホストPCとZynqをUSBで接続し電源がONになっている状態にしておきます。

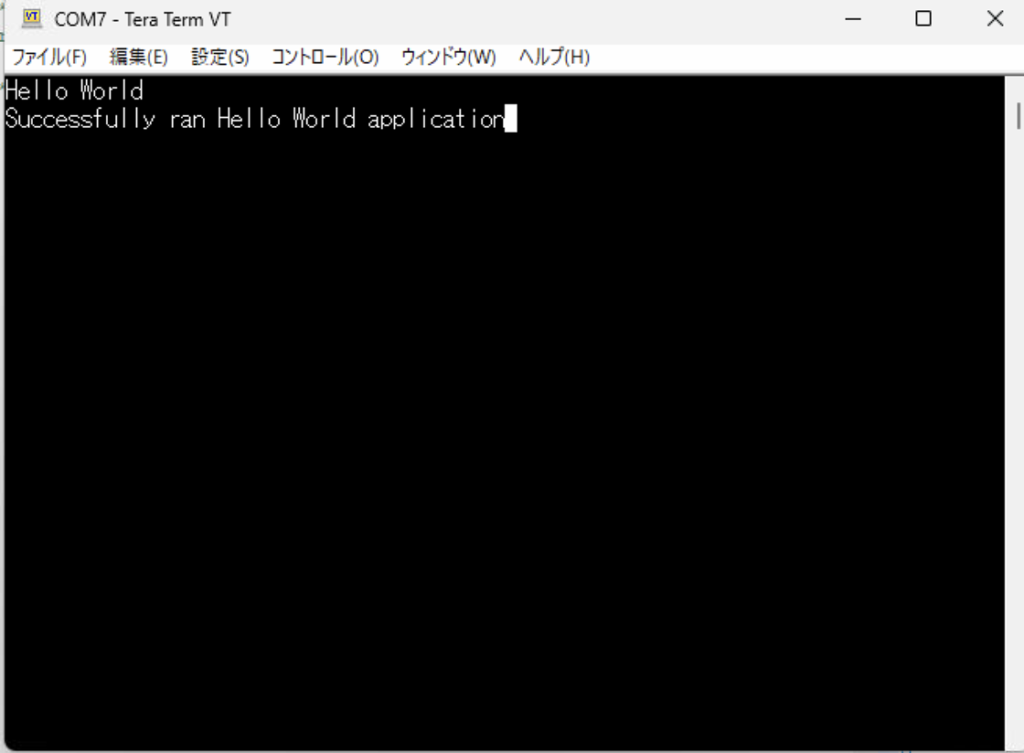

出力の確認

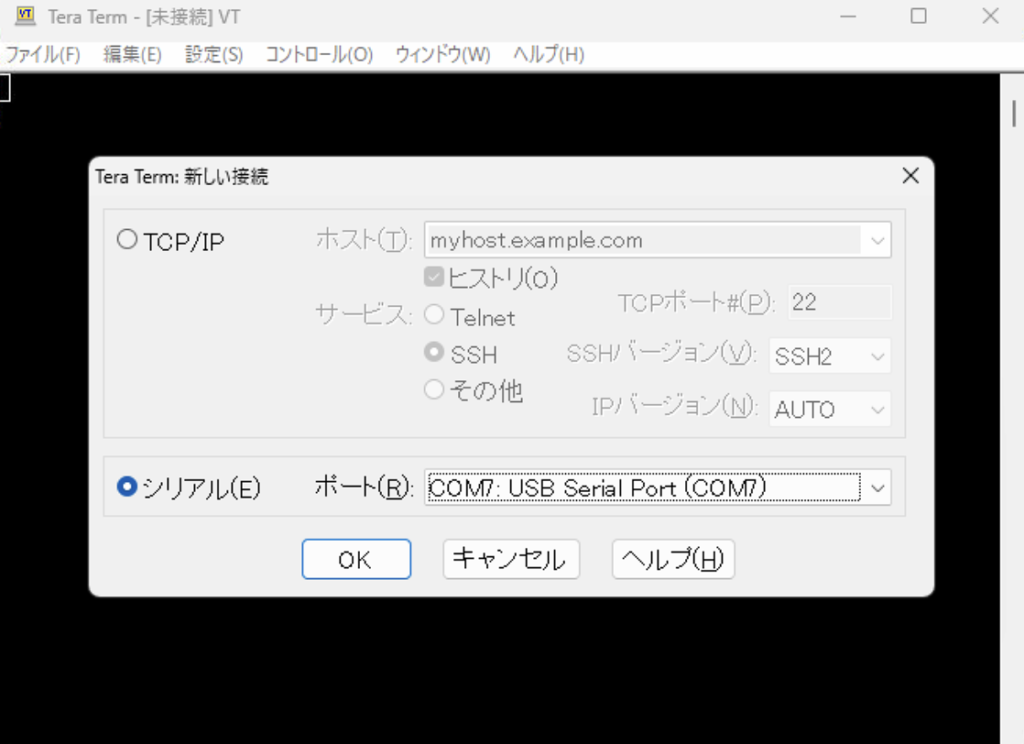

出力結果を確認するためには、TeraTermなどのソフトウェアを使用して確認する必要があります。ここでは、TeraTermを使用した確認を紹介します。シリアルを選択し、 対応するCOMポートを選択します。

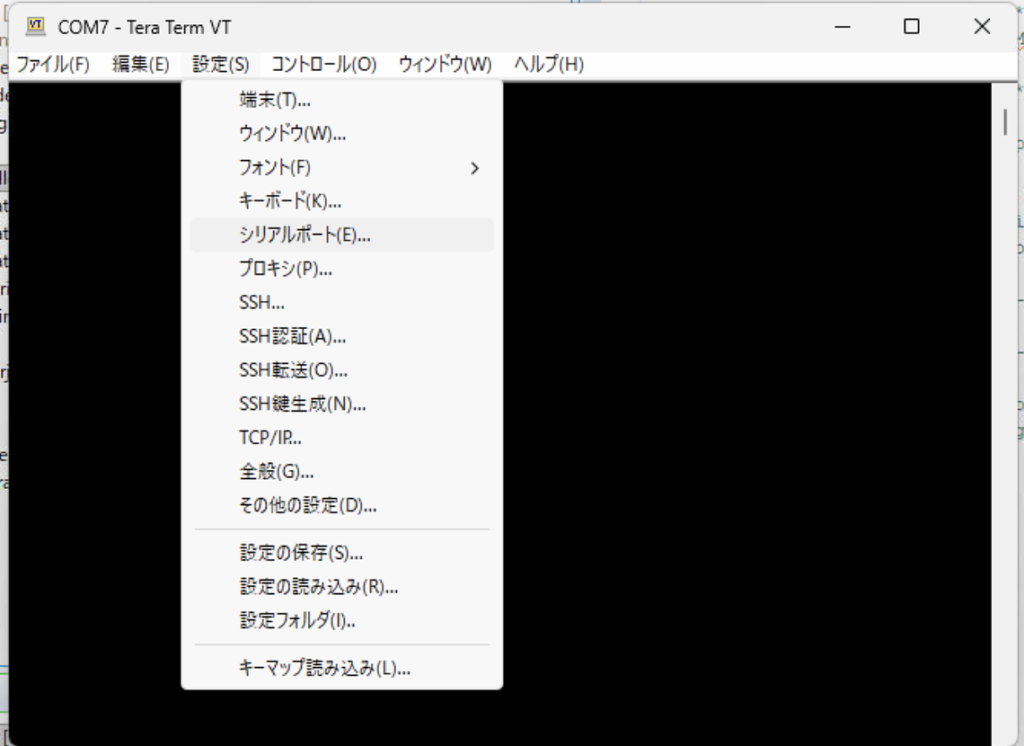

設定->シリアルポートを選択します。

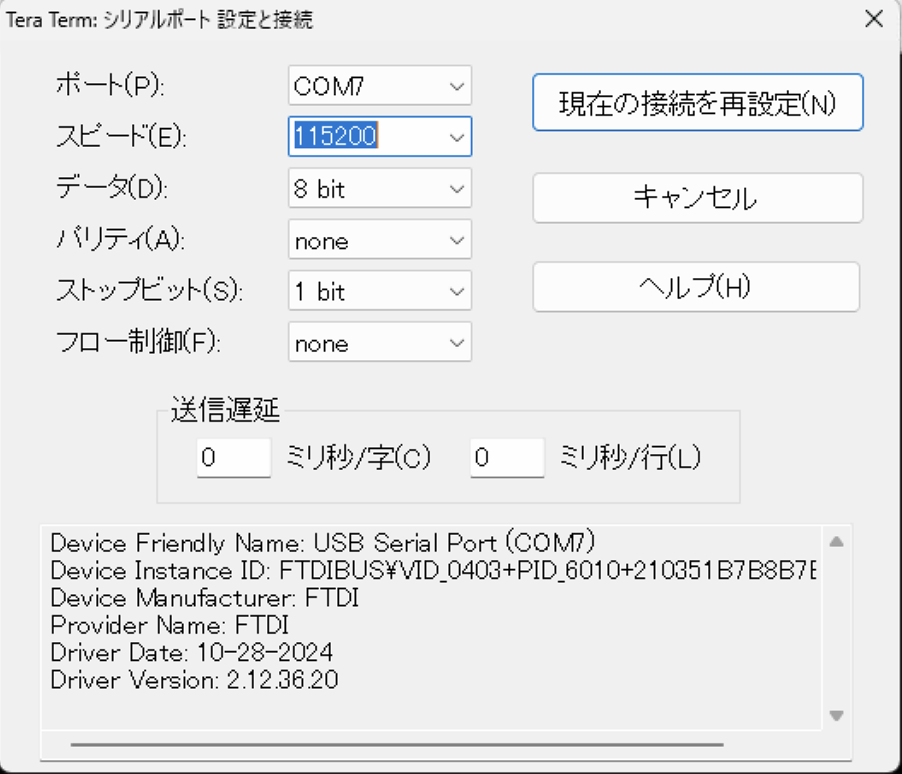

スピードを115200に変更します。他も以下と異なれば変更します。その後、現在の接続を再設定とします。これで設定は完了です。

設定が完了後、再度Run->SystemDebugger_app_systemとするとアプリが実行されます。(2回目はこちらで実行します)

実行すると、以下のようにHello Worldとアプリケーションが実行できていることが確認できました。

まとめ

本記事では、Vivado, VitisClassicを使用してZynqを動作する手順を説明しました。

コメント